PLL - phase-locked loop

PLL - phase-locked loop. Circuito elettrico ampiamente utilizzato nell'elettronica per le telecomunicazioni. Permette di creare un segnale la cui fase ha una relazione fissa con quella di un segnale di riferimento.

PLL - phase-locked loop

E N D

Presentation Transcript

PLL - phase-lockedloop Circuito elettrico ampiamente utilizzato nell'elettronica per le telecomunicazioni. Permette di creare un segnale la cui fase ha una relazione fissa con quella di un segnale di riferimento. E’ inoltre un classico esempio di applicazione all'elettronica del controllo in retroazione USI sintetizzatore di frequenza; generatore di clock, soprattutto nei sistemi a microprocessore; demodulatore FM; sistema di clock recovery, finalizzato all'estrazione del clock da un segnale aperiodico modulato. Sistemi elettronici automatici

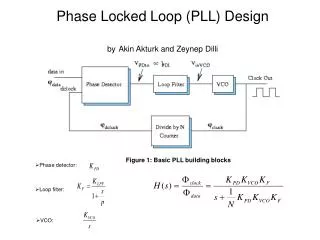

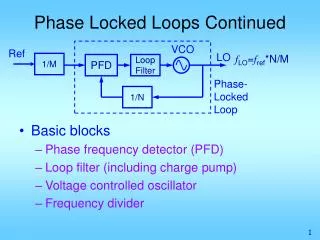

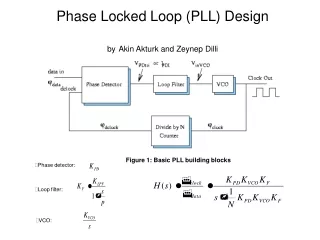

PLL - schema a blocchi Sistemi elettronici automatici

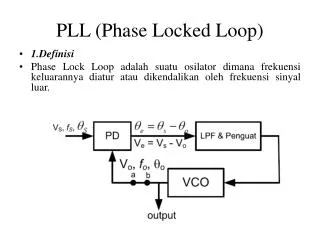

PLL - funzionamento Il segnale in ingresso e quello in uscita vengono confrontati tra loro dal comparatore di fase, che restituisce in uscita un segnale di "errore" relazionato con lo sfasamento dell'uscita rispetto all'ingresso. Se si desidera che le due oscillazioni siano accordate (stessa frequenza), è sufficiente che tale errore sia costante nel tempo. Sistemi elettronici automatici indispensabile per controllare la dinamica del sistema in retroazione e per eliminare componenti spurie in uscita dal comparatore di fase

PLL - funzionamento Il segnale di "errore", filtrato, raggiunge l'oscillatore controllato in tensione (VCO) che viene forzato a produrre un'oscillazione a una frequenza maggiore o minore a seconda dell'entità del segnale in ingresso. L'uscita del VCO è confrontata con il segnale di riferimento e a regime, il sistema tenderà a raggiungere uno stato in cui l'uscita del VCO e il segnale di riferimento hanno la stessa frequenza, ottenendo così la sintonizzazione del PLL. La velocità di risposta del circuito dipende dalle caratteristiche del filtro e del comparatore di fase e dalla sensibilità del VCO. Sistemi elettronici automatici Il divisore ricava un segnale sottomultiplo di quello generato dal VCO, ovvero con frequenza "scalata" di N, e lo riporta all'ingresso del comparatore di fase. A regime, la frequenza del segnale in uscita dal divisore (fdiv) e di quello in ingresso (fin) saranno uguali. Dato che fout = Nfdiv, a regime si avrà: fout = Nfin quindi l'uscita del VCO oscilla a una frequenza multipla di quella dell'ingresso.

PLL - rappresentazione nel dominio di Laplace L'azione del comparatore di fase risulta completamente di tipo proporzionale Sistemi elettronici automatici I PLL più semplici sono quelli in cui la funzione di trasferimento del filtro è una costante KA , cioè il filtro in realtà è un amplificatore o un attenuatore a banda larga

PLL - rappresentazione nel dominio di Laplace L'azione di controllo operata dal VCO è di tipo proporzionale-integrativa. Sistemi elettronici automatici

PLL - FdT del 1° ordine funzione di trasferimento complessiva della PLL guadagno: Sistemi elettronici automatici

Si ponga in ingresso al PLL una rampa di fase, cioè una variazione istantanea di frequenza (funzione gradino) che può essere rappresentata con una funzione di trasferimento: PLL - FdT del 1° ordine – errore a regime Ponendo in ingresso al PLL una rampa di fase, cioè una variazione istantanea di frequenza che può essere rappresentata con una funzione di trasferimento: Si ottiene come errore a regime: Sistemi elettronici automatici Il PLL mantiene un errore a regime non nullo, tanto più piccolo quanto più grande è il guadagno K. Per ottenere un errore di fase nullo sarebbe necessario un guadagno infinito, impossibile da realizzare. K non può essere aumentato a piacere, poiché è inversamente proporzionale alla banda. Se si vuole ridurre il rumore presente sul segnale d'ingresso alle alte frequenze è necessario avere un sistema a banda stretta.