Efficient Route Logic Design for Switch Networks

Learn about optimizing route logic design for switch networks to improve data transfer efficiency and reduce latency. Discover how VC Allocator and Flit Generator play key roles in improving network performance.

Efficient Route Logic Design for Switch Networks

E N D

Presentation Transcript

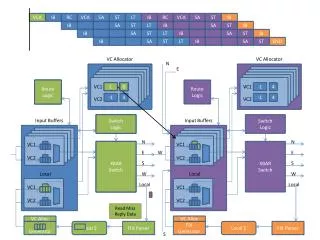

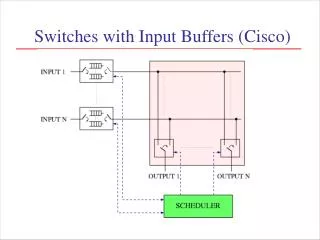

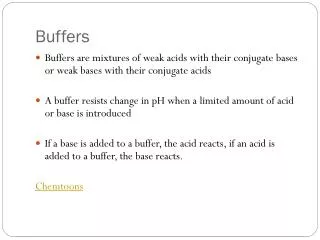

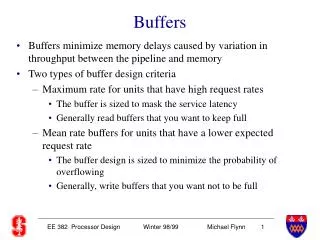

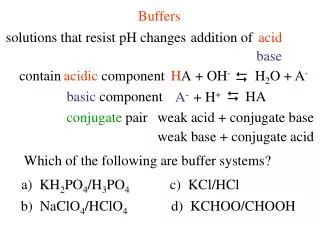

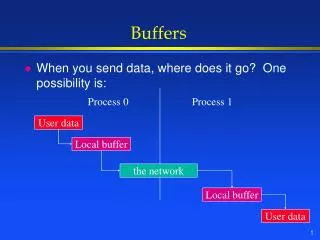

VCA IB RC VCA SA ST LT IB RC VCA SA ST IB IB SA ST LT IB SA ST IB IB SA ST LT IB SA ST IB IB SA ST LT IB SA ST END VC Allocator VC Allocator N E Route Logic Route Logic Route Logic VC1 VC1 -1 1 4 0 2 1 3 -1 4 -1 4 -1 4 VC2 VC2 Switch Logic Switch Logic Switch Logic Input Buffers Input Buffers N N VC1 VC1 XBAR Switch XBAR Switch XBAR Switch E W E VC2 VC2 S S Local W Local W Local Local VC1 VC1 VC2 VC2 Read Miss Reply Data Read Miss Forward VC Alloc VC Alloc Flit Generator Local $ Flit Parser Flit Generator Local $ Flit Parser S