CA Overview

CA Overview. Direct Mapped Cache. Accessing Direct-Mapped Cache. Set Associative Caches. Accessing Set Associative Caches. Actions on Write. Actions on Write. HW ILP. ILP. Dependency. Dependency. Dependency. Tomasulo Algorithm. Tomasulo Algorithm. Out-of-order Completion. ROB.

CA Overview

E N D

Presentation Transcript

Multiprocessor Systems • Continuous need for faster computers • shared memory model • message passing multiprocessor • wide area distributed system

Multiprocessors • Definition:A computer system in which two or more CPUs share full access to a common RAM

Bus-Based MP • Snooping cache protocols are employed • bus can be a bottleneck • limited scalability

Multistage Interconnection NW • UMA multiprocessors using multistage switching networks can be built from 2x2 switches (a) 2x2 switch (b) Message format

Non-Uniform Memory Access NUMA Multiprocessor Characteristics • Access to remote memory slower than to local • Single memory space visible to all CPUs • Access to remote memory via commands • LOAD • STORE

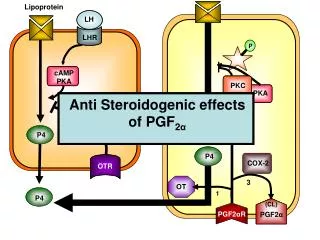

Cache Coherence Protocol • Depends on communication medium • bus-based snooping cache protocol • directory-based for MIN • Invalidation vs update • affected by lengths of write-run • cache line states usually denote • validity • write privilege • shared or private • modified (for write back)

Directory-Based MP (a) 256-node directory based multiprocessor (b) Fields of 32-bit memory address (c) Directory at node 36

Multiprocessor OS Types (1) Each CPU has its own operating system Bus

Multiprocessor OS Types (2) Master-Slave multiprocessors Bus

Multiprocessor OS Types (3) • Symmetric Multiprocessors • SMP multiprocessor model Bus

Multiprocessor Synchronization (1) • atomic TSL does not work • needs bus locking to prevent interrupts from other CPUs • busy wait with TSL may generate excessive bus traffic