Performance Analysis and Optimization of Top-Level Simulation with Parasitics in FPU Output

This study presents a comprehensive evaluation of top-level simulations incorporating all parasitic elements in a Complex chip environment. We examine the settling time and resolution in a 1.5 TeV input scenario, analyzing the impact of parasitic resistance on performance and noise issues as seen in FPPA2000. The results include worst-case plots, a detailed understanding of the Logic Input Transfer Function, and proposed optimizations. Conclusions reflect the high performance demands despite minimal transistor count, emphasizing the importance of parasitic management for verification and testing preparations.

Performance Analysis and Optimization of Top-Level Simulation with Parasitics in FPU Output

E N D

Presentation Transcript

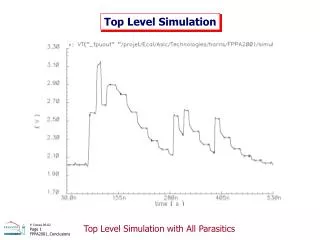

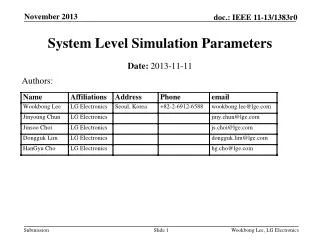

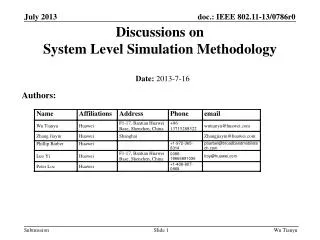

Top Level Simulation Top Level Simulation with All Parasitics

Sample at CKAD Sampled FPUout x1 Output

Reconstruct I. Subtract Ped., Gains (from sim) 1, 4.95, 8.95, 32.8 (± calc. err)

Reconstruct II. Shift by dt = 13 ns

Understanding the Results Evaluate Settling time and Resolution 1.5 TeV Input - Worst Case

Plot Modulo 25 ns Track Hold ADC

Mod 25 ns - <Hold Plateau> ADC Settling Time SH Clock Feed through Data are at 1 mV precision

Interpretation =450 µV (11 bits)

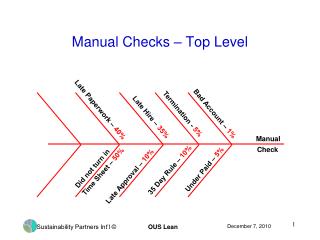

Conclusions • Complex chip: not so many transistors, but high demands on performance • Parasitic resistance really does seem to be the cause of the problems we had with FPPA2000 • FPPA2000 noise reproduced in simulation • Layout optimizations • Some circuit tweaks • Top-level simulations with all parasitics predict performance which meets specs • Consider preparation for verification and test