Placement-Coupled Logic Replication and Resynthesis

Investigating placement-coupled logic replication and resynthesis for improved circuit performance. This approach involves perturbing circuits at a physical level to optimize post-layout performance through logic replication and effective embedding techniques. Achieving significant reductions in clock period with minimal overhead. Adaptability to modern FPGA architectures and ongoing work includes application to commercial FPGAs and integrated timing optimization strategies.

Placement-Coupled Logic Replication and Resynthesis

E N D

Presentation Transcript

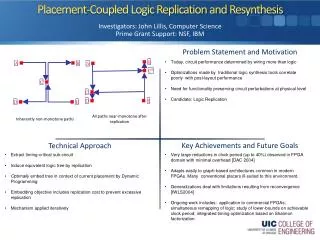

Placement-Coupled Logic Replication and Resynthesis Investigators: John Lillis, Computer Science Prime Grant Support: NSF, IBM • Today, circuit performance determined by wiring more than logic • Optimizations made by traditional logic synthesis tools correlate poorly with post-layout performance • Need for functionality preserving circuit perturbations at physical level • Candidate: Logic Replication All paths near-monotone after replication Inherently non-monotone paths • Extract timing-critical sub-circuit • Induce equivalent logic tree by replication • Optimally embed tree in context of current placement by Dynamic Programming • Embedding objective includes replication cost to prevent excessive replication • Mechanism applied iteratively • Very large reductions in clock period (up to 40%) observed in FPGA domain with minimal overhead [DAC 2004] • Adapts easily to graph-based architectures common in modern FPGAs. Many conventional placers ill-suited to this environment. • Generalizations deal with limitations resulting from reconvergence [IWLS2004] • Ongoing work includes: application to commercial FPGAs; simultaneous remapping of logic; study of lower-bounds on achievable clock period; integrated timing optimization based on Shannon factorization.