Physical Verification Signoff for DDR IP using PVS

180 likes | 560 Vues

Physical Verification Signoff for DDR IP using PVS. Tobing Soebroto, Cadence IP Group Presented at Signoff Summit Nov 21, 2013. Agenda. 1. Cadence IP Factory. 2. Signoff Challenges. 3. Why PVS for Physical Verification. 4. Conclusions. Growing IPG with the Best.

Physical Verification Signoff for DDR IP using PVS

E N D

Presentation Transcript

Physical Verification Signoff for DDR IP using PVS Tobing Soebroto, Cadence IP Group Presented at Signoff Summit Nov 21, 2013

Agenda 1. Cadence IP Factory 2. Signoff Challenges 3. Why PVS for Physical Verification 4. Conclusions

Growing IPG with the Best Building a comprehensive ecosystem… partners, customers, foundries, design houses, etc. Acquisition of key IP Tensilica joins IPG Expansion to existing Analog Team Denali joins Cadence Systems Cosmic joins IPG Evatronix to join IPG Pre - 2013 Q2 2013 Q3+ 2013 … • Denali acquisition - strong memory IP and models • Analog team – expands analog capabilities • IP acquisition provides key mobile IP technology • Tensilica adds innovative and system level IP to portfolio • Cosmic expands AMS IP and provides key mobile IP • Evatronix will complement USB and memory IP offering Cadence Confidential

Cadence IP FactoryNext Gen SoCs USB Ctrl.+PHY DRAM Ctrl.+PHY NAND Ctrl.+PHY PCIe Ctrl.+PHY Ethernet MAC+PCS+PHY MIPI Ctrl.+PHY AMS Analog Mixed Signal ADC/DAC DSI Gen1 USB 2 10/100 MAC ONFi 1/2/3 DDR1/2 DDR3 1G MAC Toggle 1/2 AFE USB 3 CSI Gen2 DDR4 10G MAC Async SENSORS USB OTG SLIMbus LPDDR1/2 Gen3 40G MAC SDIO Device PLL/DLL USB Hub DigRF LPDDR3 Gen3L1 substate 100G MAC SD/SDIO Host 1/2/3/3.2/4 LPDDR4 PVT mon HSIC BIF AVB Wide I/O M-PCIe MMC/eMMC 4.2/4.4/5.0 SERDES USB 2 PHY D-PHY Auto Ethernet Wide I/O 2 PCIe PHY Power Mgmt USB 3 PHY M-PHY 10G–KR HMC UHS – I/II

Cadence DDR PHY IPSilicon proven, highest performance PHY • Robust PHY IP ready for system integration • First to market – DDR2400, WideIO, LPDDR4 • Complete jitter analysis and char. reports • Verified with leading memory models • System Design-In Kit : PCB modeling: SI/PI analysis • HS PHY • Scalable to 3200 performance • Per bit de-skewing, per rank leveling • DDR3/4/3L, LPDDR2/3/4 support • DDR2400 silicon characterization • LP PHY • Up to 1600 performance • Lowest power/area, integrated hard controller • DDR2/3/3L LPDDR2/3 support • High volume production • IP around your chip, not other way round • 8 bit hardened slices + IO + PLL integration ready • Flexible IO ordering, bump pitch, form factor • Custom, fully hardened PHY option DFI 2.1/3.1 Interface Delay line on DQS Per-bit DQ Delay line Synthesizable PHY logic DRAM interface HS PHY IO Pads

Motivation to Develop IPs Early • With shorter design cycle, IP is a key component of the design realization • Foundry • Foundries like to work with IP companies and make available the widest range of IP to win new design customers • Cadence IP Group • Be first to market with differentiated IP • Cover a broad range of customer needs • Get as many customers fast

Signoff Challenges to Overcome • Foundry: • The IP has to developed early and be available to customers, before the new designs come for production • This requires the infrastructure to be ready early for IP companies, like rule decks, techfiles, PDKs,… • Cadence IP Group • IP products support multiple new foundries • Tools used must support leading edge technologies/process nodes for example, TSMC 16FF technologies • Must help to improve productivity and achieve fastest time to market • Design impact needs to be understood • Mixed Signal flows • Reduce debugging time • Reduce Iterations/loops to signoff

Primary Requirement: Rule Deck AvailabilityPVS History and Status • Previously • PVS rule decks were available by request to the foundry and Cadence foundry team • Now • PVS is available online at selected foundries early with other signoff tools • Decision: • PVS is our plan of record where decks are available and has been used on numerous tapeouts

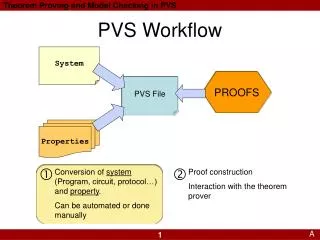

Mixed Signal Design ChallengesMixed verilog and schematic view We liked the tight integration of PVS in Virtuoso • No translation of Verilog to CDL. Verilog is read directly. • No manual translation of dfII to CDL. • No need prepare mapping for probing in dfII. • No need to merge netlists. • No need to create scripts. Convert Verilog to CDL Convert dfII to CDL + mapping Merge netlists Batch oriented submission PVS GUI submission One pass submission Significant gain for mixed analog/digital schematics

Reduced Probing Time Probing from error report to dfII. • Mixed Signal Designs input schematic is mix of dfII, Verilog and CDLs: • PVS LVS Debug Environment eases probing by providing: • From error report to dfII. • From error report to Verilog • From error report to CDL/SPICE Probing from error report to Verilog Probing from error report to CDL/SPICE

PVS ISL Facilitates One-Pass Short IsolationDebugging Time savings • Conventional way of debug • Hundreds shapes of net 122 to investigate • PVS ISL reduced the number of shapes to debug to ~10 and exactly pointed to the short.

We start Debugging While Run is in ProgressAs soon as first results are available • Conventional way of debug: thousands shapes of ground net ‘gnd’ to investigate. • PVS ISL reduced number of shapes to debug to ~30 and exactly points to short.

Conclusion • PVS is the plan of record for Cadence IP group • PVS has many technologies which ease and fasten signoff time to tapeout • In-design applications which reducing debugging time • Timing aware dummy metal fill • Interactive DRC with IPVS • Advanced node technology support • Cadence IP group have completed numerous production tape-outs with PVS