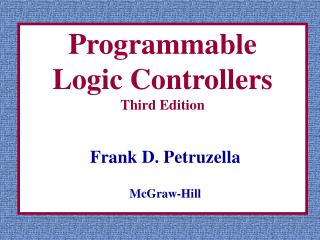

可编程逻辑器件: PLD--Programmable Logic Devices :用户构造逻辑功能。

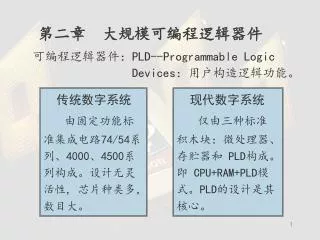

可编程逻辑器件: PLD--Programmable Logic Devices :用户构造逻辑功能。. 第二章 大规模可编程逻辑器件. 传统数字系统 由固定功能标 准集成电路 74/54 系 列、 4000 、 4500 系 列构成。设计无灵 活性 , 芯片种类多, 数目大。. 现代数字系统 仅由三种标准 积木块:微处理器、 存贮器和 PLD 构成。 即 CPU+RAM+PLD 模 式。 PLD 的设计是其 核心。. 80 年代初: Lattice 公司推出 GAL_Generic

可编程逻辑器件: PLD--Programmable Logic Devices :用户构造逻辑功能。

E N D

Presentation Transcript

可编程逻辑器件:PLD--Programmable Logic Devices:用户构造逻辑功能。 第二章 大规模可编程逻辑器件 传统数字系统 由固定功能标 准集成电路74/54系 列、4000、4500系 列构成。设计无灵 活性, 芯片种类多, 数目大。 现代数字系统 仅由三种标准 积木块:微处理器、 存贮器和 PLD构成。 即 CPU+RAM+PLD模 式。PLD的设计是其 核心。

80年代初:Lattice公司推出GAL_Generic Array Logic (第二代); §2.1 可编程逻辑器件概述 一、PLD的发展进程 70年代初:PROM、 PLA_Programmable Logic Array (第一代); 70年代末:AMD 公司推出PAL_Programmable Array Logic

90年代初:Lattice公司提出 ISP_In System Programming 概念,推出 ispLSI。 80年代中:Xilinx公司推出 FPGA_Field Programmable Gates Array; Altera公司推出EPLD_Erasable Programmable Logic Device; 近年 PLD的发展: 密度:单片已达1000万系统门 速度:达420MHz以上 线宽:已达 90 nm,属甚深亚微米技术 (VDSM—Very Deep Sub Micrometer)

高集成度; 高速度; 高可靠; 在系统编程(ISP_In System Programming ) PLD已占整个IC产值的40%以上。PLD的产量、 集成度每年增加35%,成本降低40%。 二、PLD产品的特点:

PLD工业市场份额 Total 1998 PLD Market=$2.1 B Total 1999 PLD Market=$2.6 B Source: Dataquest, March 2000

1、 从互连延时入手解决系统速度问题 门延时:几百 ns →不足 2 ns 互连延时:相对门延时越来越大 三、近年 PLD的发展热点

1)ISP(In_System Programmability/ Programming): 是指对器件、电路板、整个电子系统进 行逻辑重构和修改功能的能力。这种重构可 以在制造之前、制造过程中、甚至在交付用 户使用之后进行。 传统 PLD:先编程后装配; ISP PLD:可先编程后装配,也可先装配后 编程。 2、 在系统可编程技术(ISP)

2)ISP技术的优越性 设计修改方便,产品面市 速度快,减少原材料成本, 提高器件及板级的可测试性。 设计 减少制造成本,免去单独编程工序,免去重做印刷电路板的工作,大量减少库存,减少预处理成本,提高系统质量及可靠性。 制造 提供现场系统重构或现场系统用户化的可能,提供遥控现场升级及维护的可能 现场服务/支持

非ISP工艺流程 3)ISP技术简化生产流程比较: ISP工艺流程 从仓库提取器件 从仓库提取器件 对器件编程 焊接电路板 贴标签 编程及电路板测试 进半成品库 提取特定器件 焊接电路板 电路板测试 ISP技术对缩短生产周期,加快产品上市极为重要。

现配置时间为几十-几百ms 实时重配问题 配置时间的极大缩短: 硬件→软硬件→资源 4)ISP的进一步发展:

PLD的生产厂家众多,产品名称各异,分 类方法多样。 常见的PLD产品:PROM、EPROM、 EEPROM、 PLA、FPLA、PAL、GAL、CPLD、 EPLD、 EEPLD、HDPLD、FPGA、pLSI、 ispLSI、 ispGAL、ispGDS等。 四、PLD的种类及分类方法

低密度PLD: 高密度PLD(HDPLD):超过500门 1、根据器件密度分为: PLD 低密度的PLD,如PLA、 PROM、PAL、GAL 高密度的PLD (HDPLD)

FPGA(Field Programmable Gates Array) CPLD(Complex Programmable Logic Device) FPGA:内部互连结构由多种长度不同的连线资 源组成,每次布线的延迟可不同,属统 计型结构。逻辑单元主体为由静态存储 器(SRAM)构成的函数发生器,即查找 表。通过查找表可实现逻辑函数功能。 采用SRAM工艺。 2、根据器件互连结构、逻辑单元结构分为:

CPLD:内部互连结构由固定长度的连线资 源组成,布线的延迟确定,属确定型结构。逻 辑单元主要由“与或阵列”构成。该结构来自于 典型的PAL、GAL器件的结构。采用EEPROM工艺。 任意一个组合逻辑都可以用“与—或”表达 式来描述,所以该“与—或阵列”结构能实现大 量的组合逻辑功能。

CPLD和FPGA的主要区别: 1)结构上的不同 2)集成度的不同 CPLD:500 - 50000门; FPGA:1K – 100 M 门 3)应用范围的不同 CPLD逻辑能力强而寄存器少(1K左右), 适用于控制密集型系统;FPGA逻辑能力较弱但 寄存器多(100多K),适于数据密集型系统。 4)使用方法的不同

3、从可编程特性分为 一次性编程:PROM、PAL 重复可编程:紫外线擦除:数十次; E2CMOS工艺:上千次; SRAM结构:上万次 4、从编程元件分为 熔丝型开关; 可编程低阻电路元件; EPROM; EEPROM; SRAM;

§2.2 Altera 可编程逻辑器件 PLD(FPGA、CLPD)种类繁多,特点各异。共同之处包括三大部分: a. 一个二维的逻辑块阵列,构成了PLD器 件的逻辑核心。 b. 输入/输出块。 c. 连接逻辑块的互连资源,用于逻辑块 之间、逻辑块与输入/输出块之间的连 接。

PLD结构图 输入/输出块 逻辑块(逻辑阵列) 互连资源

CPLD与FPGA的主要区别在于逻辑块(逻辑 单元)的构成不同: CPLD的 基本逻 辑单元 如: EPM7128

FPGA的 基本逻 辑单元 如: EPF10K10 含576个 逻辑单元

一、Altera器件概述 Altera公司PLD分为两大系列: MAX MAX9000 MAX7000 MAX5000 Classic FLEX APEX II APEX20K FLEX10K FLEX8000 FLEX6000 Altera PLD系列

MAX系列: 多阵列矩阵(Multiple Array Matrix) 内部结构: 可编程的“与”阵列和固定 “或”阵列实现逻辑功能; 采用EPROM工艺(Classic、 MAX5000),或EEPROM工艺 (MAX7000、MAX9000); 属CPLD。 MAX MAX9000 MAX7000 MAX5000 Classic

FLEX系列: 灵活逻辑单元阵列 (Flexible Logic Element Matrix) 内部结构: 使用查找表(Look Up Table __LUT)结构来实现逻辑功 能;采用SRAM工艺;属 FPGA。 FLEX10K首次采用嵌入式阵列 (EAB_Embedded Array Block ) APEX20K融合查找表、乘积项、 嵌入式阵列和存贮器于一体。 FLEX APEX II APEX20K FLEX10K FLEX8000 FLEX6000

二、Altera FLEX 10K 系列器件 1、性能特点 1)工业界第一种嵌入式可编程逻辑器件系列: 嵌入式阵列(EAB_Embedded Array Block,2048位/每个EAB) 逻辑阵列(LAB_Logic Array Block) 2)高密度 最大250000门/片,40960位内部RAM (20个EAB),可实现单片集成

3)系统级特点: 多电压I/O接口、 低功耗(SRAM工艺) JTAG(Joint Test Action Group) BST(Boundary Scan Test) ICR(In Circuit Reconfiguration), 在电路可重构。 时钟锁定(Clock Lock)电路: 减小时钟延迟和偏移 时钟自举(Clock Boost)电路: 时钟倍频低变形,时钟树形分配网络

4)灵活的内部连接 快速通道(Fast Track): 连续式布线结构 特点:延迟可预测 专用进位链: 高速加法器、 计数器、 比较器 专用级联链: 实现高速、多输入逻辑函数。

5)增强功能的 I/O引脚 I/O脚三态输出使能控制 I/O脚漏极开路选择 (Open-Drain Option) 输出电压摆率控制: 高速、或低噪声 6)多种封装形式,多种器件类型 84 - 672引脚,相同封装引脚兼容

2、功能描述 嵌入式阵列块(EAB)、逻辑阵列块(LAB)、 Fast Track、I/O单元

3、嵌入式阵列块:EAB(Embedded Array Block) 1)EAB结构: RAM: 2048 bit; 数据线: 8bit(max); 地址线: 11bit(max) EAB 模块图

EAB 可用于实现: FIFO、ROM、RAM、 乘法器、 数字滤波器、 微处理器 利用输入输出可编程寄存器EAB可实现: 同步设计、 异步设计