Buffer Manager Pre-Prototype Design for BTeV Collaboration

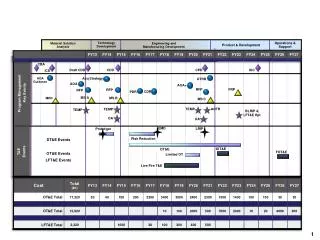

This document outlines the Buffer Manager design for the BTeV collaboration, focusing on the pre-prototype developed by Jinyuan Wu in June 2002. It encompasses data paths, including the connections and operations between the PTA, FIFO, and DSP components. Key features such as header verification, data formatting (16 bits data word + 15 bits timestamp), and the rotation priority selection scheme are detailed. The architecture supports significant data combinations, necessitating advanced management for efficient operation over extensive timeframes, estimating a match requires 10,000 years at a rate of 7 MHz.

Buffer Manager Pre-Prototype Design for BTeV Collaboration

E N D

Presentation Transcript

Buffer Manager for Pre-prototype Jinyuan Wu For BTeV collaboration June. 2002

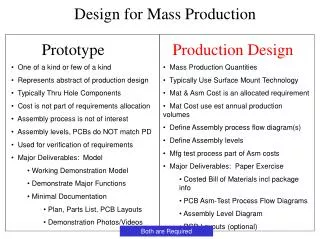

Data Path of Buffer Manager • PTA to FIFO to DSP • DSP to PTA

InBuff DSP0 FIFO OutBuff Header Check Header InBuff DSP1 0 2 1 DSPSEL S4STEPS OutBuff 3 DSP2 Count & Flag DSP3

Data Format DATA Word Count: 16 bits + Time Stamp: 15 bits 89abcdef Header: 64 bits total 76543210 16x10^18 combinations at 7 MHz need 2x10^12 sec to match, i.e. 10,000 years

Rotation Priority Selection DSP0 DSP0 DSP0 DSP0 DSP1 DSP1 DSP1 DSP1 DSP2 DSP2 DSP2 DSP2 DSP3 DSP3 DSP3 DSP3

DSP Loading (Using priority selection scheme) (Using rotation priority selection scheme) DSP0 DSP1 DSP2 DSP3

InBuff DSP0 FIFO OutBuff Header Check Header InBuff DSP1 OBFSEL S4STEPS OutBuff DSP2 PTA DSP3

Loop Back • DSP-in-DSP-out • PTA-in-PTA-out • Dummy cable for PTA-out-PTA-in • Dummy module for DSP-out-DSP-in

PTA InBuff DSP0 FIFO OutBuff Header Check Header InBuff DSP1 OBFSEL S4STEPS OutBuff DSP2 PTA DSP3

Cascade Pre-prototype • PTA out of pre-prototype #1 to PTA in of pre-prototype #2

PTA PTA FIFO FIFO Header Check Header Header Check Header OBFSEL S4STEPS OBFSEL S4STEPS PTA PTA

The End Thanks