Reliable Binary Signed Digit Number Adder Design

This paper presents a design for a reliable binary signed digit number adder, focusing on carry-free addition methods. The work examines existing literature on fast adder architectures, including carry-skip, carry-lookahead, and limited carry-free adders. It covers the synthesis results, highlighting performance metrics such as propagation delay, area, and power consumption. Key findings indicate that carry-free addition can facilitate multiple arithmetic operations efficiently, with various coding schemes impacting complexity and timing. This design aims to optimize addition processes in digital systems.

Reliable Binary Signed Digit Number Adder Design

E N D

Presentation Transcript

Reliable Binary Signed Digit Number Adder Design Han Liu Supervisor: Seok-Bum Ko Electrical & Computer Engineering Department 2010-Feb-23

Outline • Information of literature • Background • Carry Free Adder • Limited Carry Free Adder • Synthesis Result • Conclusion

Information of literature Reliable Binary Signed Digit Number Adder Design F. Kharbash, G. M. Chaudhry IEEE Computer Society Annual Symposium on VLSI(ISVLSI'07)

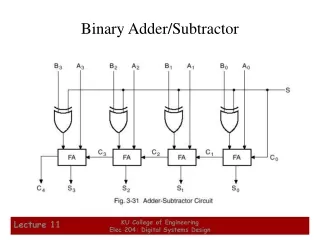

Background Fast Adder Architecture • Carry Skip Adder • Carry Look-ahead Adder • Carry Save Adder • Carry Free Adder • Limited Carry Free Adder

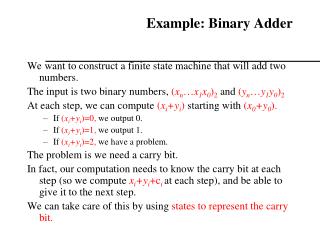

Carry Free Addition 1/4 Redundancy • Representation of numbers is not unique • Redundancy may result from narrowing the range of represented values (e.g. 1's compl.) • Redundancy may result from adopting the digit set wider than radix ({-1,0,1} in radix 2) • Conversion is a carry-propagate (slow) process

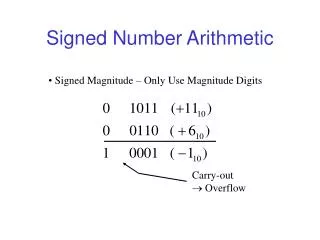

Carry Free Addition 2/4 Reduction of digit set by carry propagation by only one position P=10*T+W P is preliminary results T is transfer digits W is immediate sums

Carry Free Addition 3/4 Two-Stage Carry Free Adder

Carry Free Addition 4/4 Coding Schemes influence on complexity • sign+value • BSD: -1 (11), 0 (00), 1 (01) • 2's complement • BSD: -1 (11), 0 (00), 1 (01) • negative-positive flags ([-1,1] only) • BSD: -1 (10), 0 (00), 1 (01) • 1-out-of-n • BSD: -1 (100), 0 (010), 1 (001)

Limited Carry Free Addition 1/3 When redundancy is not enough, the free carry propagation cannot be guaranteed 1 0 X 1 0 2 0 1 Y 0 1 1 ? 1 p 1 1 -1 e H 1 w -1 1 t 1 0 ? -1 S 1 -1 1 3 4 -2 1

Limited Carry Free Addition 2/3 Three -Stage Limited Carry Free Adder

Limited Carry Free Addition 3/3 1-out-of-3 SD number

Synthesis Result 1/2 unit is nS Timing Delay Statistic under 0.18 um technology

Synthesis Result 2/2 Area and Power Consumption Statistic

Conclusion • Propagation delay in Carry Free Adder is independent with input bit width • Different coding schemes have different complexity and timing delay • Conversion after the CFA still generate delay • CFA is suitable in multiple addition stages process • CFA is suitable if redundancy is enough (ie. BCD number in decimal addition)

Question Thanks!