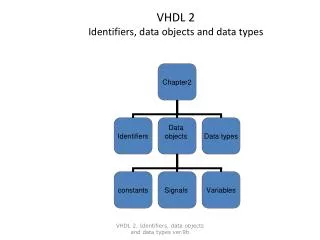

VHDL Data Types

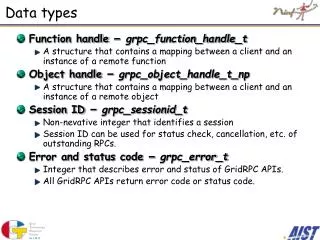

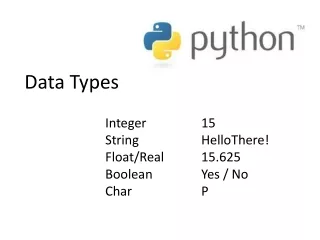

VHDL Data Types. Module F3.1. VHDL Data Types. Scalar Integer Enumerated Real (floating point)* Physical* Composite Array Record Access (pointers)*. * Not supported by synthesis tools. VHDL Data Objects. Constant Variable Signal File*. * Not supported by synthesis tools.

VHDL Data Types

E N D

Presentation Transcript

VHDL Data Types Module F3.1

VHDL Data Types • Scalar • Integer • Enumerated • Real (floating point)* • Physical* • Composite • Array • Record • Access (pointers)* * Not supported by synthesis tools

VHDL Data Objects • Constant • Variable • Signal • File* * Not supported by synthesis tools

Identifiers • May contain A-Z, a-z, 0-9, _ • Must start with letter • May not end with _ • May not include two consecutive _ • VHDL is case insensitive • Sel sel and SEL refer to same object

Identifier Examples • A2G • valid • 8bit_counter • invalid -- starts with number • _NewValue • invalid -- starts with _ • first# • invalid -- illegal character

Characters and Strings • Characters • ‘A’, ‘0’, ‘1’, ‘$’, ’x’, ‘*’ • Strings • “string of characters” • “00101101” • “0X110ZZ1”

Characters and Strings • Bit Strings • B”011111010110” • O”3726” • X”7D6”

Integer Data Type • Integer • Minimum range for any implementation as defined by standard: - 2,147,483,647 to 2,147,483,647 • Example assignments to a variable of type integer : ARCHITECTURE test_int OF test IS BEGIN PROCESS (X) VARIABLE a: INTEGER; BEGIN a := 1; -- OK a := -1; -- OK a := 1.0; -- illegal END PROCESS; END test_int;

Integer Data Type • Minimum range for any implementation: - 2,147,483,647 to 2,147,483,647 • Define range of integer • minimizes synthesized logic • type CountValue isrange 0 to 15; • type Twenties isrange 20 to 29; • type Thirties isrange 39 downto 30; • Range should start with 0 • Synthesis tools use number of bits as if starting at 0

Example of Integer Data Type process(addr) variable j: integer range 0 to 35; variable addru: unsigned(7 downto 0); begin for i in 7 downto 0 loop addru(i) := addr(i); end loop; j := conv_integer(addru); M <= rom(j); end process;

VHDL Data TypesScalar Types (Cont.) • Enumerated • User specifies list of possible values • Example declaration and usage of enumerated data type : TYPE binary IS ( ON, OFF ); ... some statements ... ARCHITECTURE test_enum OF test IS BEGIN PROCESS (X) VARIABLE a: binary; BEGIN a := ON; -- OK ... more statements ... a := OFF; -- OK ... more statements ... END PROCESS; END test_enum;

VHDL Data TypesScalar Types (Cont.) • Real • Minimum range for any implementation as defined by standard: -1.0E38 to 1.0E38 • Example assignments to a variable of type real : ARCHITECTURE test_real OF test IS BEGIN PROCESS (X) VARIABLE a: REAL; BEGIN a := 1.3; -- OK a := -7.5; -- OK a := 1; -- illegal a := 1.7E13; -- OK a := 5.3 ns; -- illegal END PROCESS; END test_real;

VHDL Data TypesScalar Types (Cont.) • Physical • Require associated units • Range must be specified • Example of physical type declaration : • Time is the only physical type predefined in VHDL standard TYPE resistance IS RANGE 0 TO 10000000 UNITS ohm; -- ohm Kohm = 1000 ohm; -- i.e. 1 KW Mohm = 1000 kohm; -- i.e. 1 MW END UNITS;

Booleans type boolean is (false, true); variable A,B,C: boolean; C := not A C := A and B C := A or B C := A nand B C := A nor B C := A xor B C := A xnor B

Bits type bit is (‘0’, ‘1’); signal x,y,z: bit; x <= ‘0’; y <= ‘1’; z <= x and y;

Standard Logic library IEEE; use IEEE.std_logic_1164.all; type std_ulogic is ( ‘U’, -- Uninitialized ‘X’ -- Forcing unknown ‘0’ -- Forcing zero ‘1’ -- Forcing one ‘Z’ -- High impedance ‘W’ -- Weak unknown ‘L’ -- Weak zero ‘H’ -- Weak one ‘-’); -- Don’t care

Standard Logic typestd_ulogicis unresolved. Resolved signals provide a mechanism for handling the problem of multiple output signals connected to one signal. subtype std_logic is resolved std_ulogic;

Attributes • Attributes provide information about certain items in VHDL, e.g : • Types, subtypes, procedures, functions, signals, variables, constants, entities, architectures, configurations, packages, components • General form of attribute use : • VHDL has several predefined, e.g : • X'EVENT -- TRUE when there is an event on signal X • X'LAST_VALUE -- returns the previous value of signal X • Y'HIGH -- returns the highest value in the range of Y • X'STABLE(t) -- TRUE when no event has occurred on signal X in the past ‘t’ time name'attribute_identifier -- read as “tick”

Operators • Operators can be chained to form complex expressions, e.g. : • Can use parentheses for readability and to control the association of operators and operands • Defined precedence levels in decreasing order : • Miscellaneous operators -- **, abs, not • Multiplication operators -- *, /, mod, rem • Sign operator -- +, - • Addition operators -- +, -, & • Shift operators -- sll, srl, sla, sra, rol, ror • Relational operators -- =, /=, <, <=, >, >= • Logical operators -- AND, OR, NAND, NOR, XOR, XNOR res <= a AND NOT(B) OR NOT(a) AND b;

0 31 ...element indices... 0 1 ...array values... VHDL Data TypesComposite Types • Array • Used to group elements of the same type into a single VHDL object • Range may be unconstrained in declaration • Range would then be constrained when array is used • Example declaration for one-dimensional array (vector) : TYPE data_bus IS ARRAY(0 TO 31) OF BIT; VARIABLE X : data_bus; VARIABLE Y : BIT; Y := X(12); -- Y gets value of element at index 12

VHDL Data TypesComposite Types (Cont.) • Example one-dimensional array using DOWNTO : • DOWNTO keyword must be used if leftmost index is greater than rightmost index • ‘Big-endian’ bit ordering, for example TYPE reg_type IS ARRAY(15 DOWNTO 0) OF BIT; 15 0 ...element indices... 0 1 ...array values... VARIABLE X : reg_type; VARIABLE Y : BIT; Y := X(4); -- Y gets value of element at index 4

VHDL Data TypesComposite Types (Cont.) • Records • Used to group elements of possibly different types into a single VHDL object • Elements are indexed via field names • Examples of record declaration and usage : TYPE binary IS ( ON, OFF ); TYPE switch_info IS RECORD status : BINARY; IDnumber : INTEGER; END RECORD; VARIABLE switch : switch_info; switch.status := ON; -- status of the switch switch.IDnumber := 30; -- e.g. number of the switch