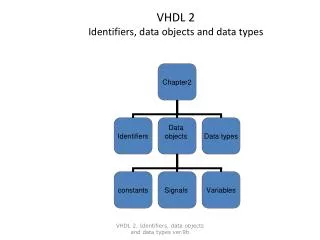

VHDL 2 Identifiers, data objects and data types

VHDL 2 Identifiers, data objects and data types. Identifiers. How to create names?. Identifiers. Used to represent an object (constant, signal or variable ,entity, architecture) Two types Basic identifier Extended identifier. Rules for Basic Identifiers.

VHDL 2 Identifiers, data objects and data types

E N D

Presentation Transcript

VHDL 2Identifiers, data objects and data types VHDL 2. Identifiers, data objects and data types ver.9b

Identifiers • How to create names? VHDL 2. Identifiers, data objects and data types ver.9b

Identifiers • Used to represent an object (constant, signal or variable ,entity, architecture) • Two types • Basic identifier • Extended identifier VHDL 2. Identifiers, data objects and data types ver.9b

Rules for Basic Identifiers • Names for users to identify data objects: signals, variables etc. • First character must be a letter • last character cannot be an underscore • Not case sensitive • Two connected underscores are not allowed • Examples of identifiers: a, b, c, axy, clk ... VHDL 2. Identifiers, data objects and data types ver.9b

Example: a,b,equals are Identifiers of signals • 1 entity eqcomp4 is • 2 port (a, b: in std_logic_vector(3 downto 0); • 3 equals: out std_logic); • 4 end eqcomp4; • 5 • 6 architecture dataflow1 of eqcomp4 is • 7 begin • 8 equals <= '1' when (a = b) else '0’; • 9--“comment” equals is active high • 10 end dataflow1; VHDL 2. Identifiers, data objects and data types ver.9b

Extended Identifier • They were add in VHDL’93 in order to make the code more compatible with tools. Characteristics: • Contain special characters • Begin with numbers • Same name as keywords • Start with (/),followed by a sequence of characters ,followed by another backslash(/) • Case sensitive VHDL 2. Identifiers, data objects and data types ver.9b

Examples • /a+b/ • /3 state/ • /type/ • Entity example is port(in_port: in bit; Bit_port:out bit); End example VHDL 2. Identifiers, data objects and data types ver.9b

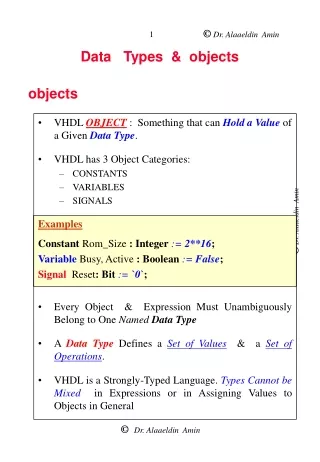

Data objects VHDL 2. Identifiers, data objects and data types ver.9b

Data objects • Constant • Signals • variables VHDL 2. Identifiers, data objects and data types ver.9b

Data objects: 3 different objects • 1 Constants: hold values that cannot be changed within a design. • e.g. constant width: integer 8 • 2 Signals: to represent wire connections • e.g. signal count: bit_vector (3 downto 0) • -- count means 4 wires; they are count(3),count(2), count(1), count(0). • 3 Variables: internal representation used by programmers; do not exist physically. VHDL 2. Identifiers, data objects and data types ver.9b

Recall: if a signal is used as input/output declared in port • It has 4 modes e.g. entity eqcomp4 is port (a, b: in std_logic_vector(3 downto 0 ); equals: out std_logic); end eqcomp4; VHDL 2. Identifiers, data objects and data types ver.9b

Syntax to create data objects In entity declarations VHDL 2. Identifiers, data objects and data types ver.9b

Constants with initialized values • constant CONST_NAME: <type_spec> := <value>; • -- Examples: • constant CONST_NAME: BOOLEAN := TRUE; • constant CONST_NAME: INTEGER := 31; • constant CONST_NAME: BIT_VECTOR (3 downto 0) := "0000"; • constant CONST_NAME: STD_LOGIC := 'Z'; • constant CONST_NAME: STD_LOGIC_VECTOR (3 downto 0) := "0-0-"; -- ‘-’ is don’t care VHDL 2. Identifiers, data objects and data types ver.9b

Signals with initialized values • signal sig_NAME: type_name [: init. Value]; • -- examples • signal s1_bool : BOOLEAN; -- no initialized value • signal xsl_int1: INTEGER :=175; • signal su2_bit: BIT :=‘1’; • BY DEFAULT value T’LEFT (leftmost value i.e false) VHDL 2. Identifiers, data objects and data types ver.9b

Variables with initialized values • variable V_NAME: type_name [: init. Value]; • -- examples • variable v1_bool : BOOLEAN:= TRUE; • variable val_int1: INTEGER:=135; • variable vv2_bit: BIT; -- no initialized value VHDL 2. Identifiers, data objects and data types ver.9b

Signal and variable assignments • SIG_NAME <= <expression>; • VAR_NAME :=<expression>; VHDL 2. Identifiers, data objects and data types ver.9b

Exercise 2.1: Find identifiers, I/O signals, variables, constants, arrays, and list their data_types. • 1-- a, b: out bit: • 2-- CLK, ASYNC ,LOAD, : in STD_LOGIC; • 3-- DIN: in STD_LOGIC_VECTOR(3 downto 0); • 4-- DOUT: out STD_LOGIC_VECTOR(3 downto 0); • 5 process (CLK, ASYNC) • 6 begin • 7 if ASYNC='1' then • 8 DOUT <= "0000"; • 9 elsif CLK='1' and CLK'event then • 10 if LOAD='1' then • 11 DOUT <= DIN; • 12 end if; • 13 end if; • 14 end process VHDL 2. Identifiers, data objects and data types ver.9b

Data types VHDL 2. Identifiers, data objects and data types ver.9b

Data types • User can design the type for a data object. • E.g. a signal can have the type ‘bit’ • E.g. a variable can have the type ‘type std_logic’ • Only same type can interact. VHDL 2. Identifiers, data objects and data types ver.9b

Exercise 2.2:declare a signal with type bit in line 2 • 1 Architecture test2_arch of test2 • 2 ??????????? • 3 begin • 4 ... • 5 … • 6 end test_arch For the type 'bit' it can only be '1' or '0' VHDL 2. Identifiers, data objects and data types ver.9b

Exercise 2.3: Where to specify the types for signals. Draw the schematic of this circuit. • 1 entity nandgate is • 2 port (in1, in2: in STD_LOGIC; • 3 out1: out STD_LOGIC); • 4 end nandgate; • 5 architecture nandgate_arch of nandgate is • 6 signal connect1: STD_LOGIC; • 7 begin • 8 connect1 <= in1 and in2; • 9 out1<= not connect1; • 10 end nandgate_arch; • Specify types of signals in either • port declaration, or • before ‘begin’ in architecture body VHDL 2. Identifiers, data objects and data types ver.9b

Types must match Different types : bit and std_logic • 1 entity test is port ( • 2 in1: in bit; • 3 out1: out std_logic ); • 4 end test; • 5 architecture test_arch of test is • 6 begin • 7 out1<=in1; • 8 end test_arch; Not allowed VHDL 2. Identifiers, data objects and data types ver.9b

Revision (so far we learned) • Data object • Constants, signal, Variables • Signal in port (external pins) • In • Out • Inout • Buffer VHDL 2. Identifiers, data objects and data types ver.9b

Exercise 2.4: RevisionWhat kinds of data objects are in1 and out1?What is the data type for signal out1? • 1 entity nandgate is • 2 port (in1, in2: in STD_LOGIC; • 3 out1: out STD_LOGIC); • 4 end nandgate; • 5 architecture nandgate_arch of nandgate is • 6 signal connect1: STD_LOGIC; • 7 begin • 8 connect1 <= in1 and in2; • 9 out1<= not connect1; • 10 end nandgate_arch; • Specify types of signals in either • port declaration, or • before ‘begin’ in architecture body VHDL 2. Identifiers, data objects and data types ver.9b

Different data types VHDL 2. Identifiers, data objects and data types ver.9b

Different data types VHDL 2. Identifiers, data objects and data types ver.9b

Data types VHDL 2. Identifiers, data objects and data types ver.9b

Scalar type • Is a type whose values have no elements. • Values cannot contain composite elements. • All values are in order.Each value of discrete or numeric have positional number associated with it. VHDL 2. Identifiers, data objects and data types ver.9b

Enumerated Types • An enumeration type is defined by listing (enumerating) all possible values explicitly. • Declaration Format: • TYPE type_name IS (enumeration_ident_list); type std_ulogic is (‘U’,’0’,’1’,’Z’,’W’,’L’,’H’,’-’); • then we can declare signal carry : std_ulogic:=‘U’; • The definition explicitly enumerates all possible values that an object of this type can assume User defined values consisting of identifiers, character literals. VHDL 2. Identifiers, data objects and data types ver.9b

Predefined enumeration types • TYPE bit IS (`0','1'); • TYPE boolean IS (false,true); • TYPE severity_level IS (note,warning,error,failure); • TYPE character IS (`a','b','c',...); VHDL 2. Identifiers, data objects and data types ver.9b

More Examples • TYPE Two_level_logic IS (`0','1'); • TYPE Three_level_logic IS (`0','1','Z'); • TYPE micro_op IS load,add,sub,mul); • TYPE Opcode IS (Add,Add_with_carry,Sub,Sub_with_carry,Complement); VHDL 2. Identifiers, data objects and data types ver.9b

Difference between “to” and “downto” • Given: • signal a : std_logic_vector( 2 downto 0); • Create a 3-bit bus c using “to”instead of “downto” in the declaration. • Draw the circuit for this statement: c<=a; VHDL 2. Identifiers, data objects and data types ver.9b

Answer • signal c : std_logic_vector(0 to 2); • c<=a; means c(0)<=a(2), c(1)<=a(1), c(2)<=a(0), VHDL 2. Identifiers, data objects and data types ver.9b

Exercises exercise • Declare an emulation type of the traffic light. • Declare an emulation type of the outcome of rolling a dice. • Declare an emulation type of the 7 notes of music. • Answer:type traffic_light is (yellow, green, red, yellow_green); • signal tr1: traffic_light; -- so tr1 is a signal and can be one of the 4 cases. VHDL 2. Identifiers, data objects and data types ver.9b

Integer type • Integers are the unbounded set of positive and negative whole numbers. • 32 bit limitation restricts range. • Upper and lower range constraints must be integer range. • • Declaration format: • TYPE type_name IS RANGE int_range_constraint; • • Predefined integer type: • TYPE integer IS RANGE –2147483648=[ -2 (31) ] TO 2147483647 = [2 (31) -1]; VHDL 2. Identifiers, data objects and data types ver.9b

Integer type (depends on your tool; it uses large amount of logic circuits for the implementation of integer/float operators) E.g. • Maximum range from -(2^31-1) to (2^31-1) • e.g. • variable a: integer range -255 to 255 VHDL 2. Identifiers, data objects and data types ver.9b

Floating type • Floating Points are the unbounded set of positive and negative numbers which contain a decimal point. • 32 bit limitation restricts range. • Upper and lower range constraints must contain a decimal point. • • Declaration format: • TYPE type_name IS RANGE range_constraint; • • Predefined floating point type: • TYPE real IS RANGE -1.79769E308 TO 1.79769E308; VHDL 2. Identifiers, data objects and data types ver.9b

Floating type • -1.0E38 to 1.0E38 • For encoding floating numbers, but usually not supported by synthesis tools of programmable logic because of its huge demand of resources. VHDL 2. Identifiers, data objects and data types ver.9b

Physical type • Describes objects in terms of a base unit, multiples of base unit, and a specified range. • Declaration format: • TYPE type_name IS RANGE range_constraints • UNITS • base_unit; • [ -- multiples;] • END UNITS;

Examples • Predefined physical type: • TYPE time IS RANGE -2**(31-1) TO 2**(31-1) • UNITS • fs; --femtosecond =10-15 sec • ps = 1000 fs; --picosecond =10-12 sec • ns = 1000 ps; --nanosecond =10-9 sec • us = 1000 ns; --microsecond =10-6 sec • ms = 1000 us; --millisecond =10-3 sec • sec =1000 ms; --second VHDL 2. Identifiers, data objects and data types ver.9b

Example cont… • min =60 sec; --minute • hr =60 min; --hour • END UNITS; • Example: • TYPE Resistance IS RANGE 1 TO 10E9 • UNITS • ohm; --the base unit. • kohm=1000 ohm; --secondary unit, multiple of base unit. • END UNITS; VHDL 2. Identifiers, data objects and data types ver.9b

Boolean, Bit Types • Boolean (true/false), character, integer, real, string, these types have their usual meanings. In addition, VHDL has the types: bit, bit_vector, • The type “bit” can have a value of '0' or '1'. A bit_vector is an array of bits. VHDL 2. Identifiers, data objects and data types ver.9b

Examples of some common types • Type BOOLEAN is (FALSE, TRUE) • type bit is (‘0’ ,’1’); • type character is (-- ascii string) • type INTEGER is range of integer numbers • type REAL is range of real numbers VHDL 2. Identifiers, data objects and data types ver.9b

Std_ulogic standard • Type STD_ULOGIC, defined in the package STD_LOGIC_1164,is an enumeration type as: • (‘U’--- uninitialized • ‘x’--- forcing unknown • ‘0’--- forcing 0 • ‘1’--- forcing 1 • ‘z’--- high impedance • ‘w’---weak unknown • ‘L’---Weak 0 • ‘H’--- Weak 1 • ‘-’--- Don’t care); VHDL 2. Identifiers, data objects and data types ver.9b

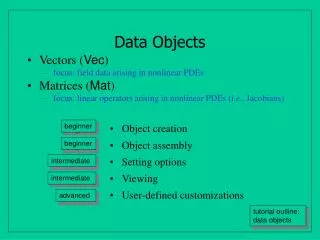

Define Array or a bus VHDL 2. Identifiers, data objects and data types ver.9b

Array type • Multiple values of same type under single identifier. • • One or more dimensions • Values referenced by indices. • Indices type must be integer or enumeration. • • Declaration format: • TYPE array_type_name IS ARRAY range_constraints) OF type; • • Predefined array types: • TYPE string IS ARRAY (positive RANGE <>) OF character; • TYPE bit_vector IS ARRAY (natural RANGE <>) OF bit; VHDL 2. Identifiers, data objects and data types ver.9b

Example: • TYPE Column IS RANGE 1 TO 80; • TYPE Row IS RANGE 1 TO 24; • TYPE Matrix IS ARRAY (Row,Column) OF boolean; VHDL 2. Identifiers, data objects and data types ver.9b

Constrained or unconstrained. • Boundaries of constrained array are stated: • TYPE array_1 IS ARRAY (integer RANGE -10 TO 25) OF bit; • TYPE array_1_too IS ARRAY (-10 TO 25) OF bit; • (NOTE: integer is optional) • • Boundaries of unconstrained array are left open: • TYPE array_2 IS ARRAY (integer RANGE <>) OF bit; VHDL 2. Identifiers, data objects and data types ver.9b

Array Subtypes: • Subsets of specified array types. • Do not define a new array type. • TYPE that SUBTYPE is based on must be an unconstrained array. • Declaration format: • SUBTYPE name IS (array_name RANGE range_constraint); • Example: • TYPE data IS ARRAY (natural RANGE <>) OF bit; • SUBTYPE low_range IS (data RANGE 0 TO 7); • SUBTYPE high_range IS (data RANGE 8 TO 15); VHDL 2. Identifiers, data objects and data types ver.9b

Advantage of subtypes • There are several advantages of subtypes. The primary advantage is to clarify what is being done in the model. They make it easier to visualize what is being stored and why by breaking large groupings of values into smaller groupings. Each "smaller grouping" can have a name which more descriptively tells what values it represents. VHDL 2. Identifiers, data objects and data types ver.9b