Ch 9. Memory, CPLDs, and FPGAs

650 likes | 946 Vues

Ch 9. Memory, CPLDs, and FPGAs. 1. Read-Only Memory. Az : output polarity control Az = 0 output active low Az = 1 output active high. 9.1.1 Using ROMs for “Random” Combinational Logic Function. 9.1.1 Using ROMs for “Random” Combinational Logic Function.

Ch 9. Memory, CPLDs, and FPGAs

E N D

Presentation Transcript

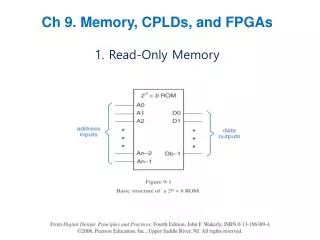

Ch 9. Memory, CPLDs, and FPGAs 1. Read-Only Memory

Az : output polarity control Az = 0 output active low Az = 1 output active high

9.1.2 Internal ROM Structure If diode present, 1 Otherwise, Ø

9.1.2 Internal ROM Structure Diodes are missing, then D3 – D0 = 0111 instead of 0010

9.1.3 Two-Dimensional Decoding To reduce decoding complexity -> 7 to 128 decoder is huge -> instead, 3 – to 8 decoder + 16 – to – 1 MUX

9.1.3 Two-Dimensional Decoding If tr exist, 1 Otherwise, Ø

9.1.5 ROM Control Inputs and Timing Three state bus OE : output enable CS : chip select OE & CS must be assecped 32k x 8bit ROM x 4 = 128kbytes (= 215 x 4 = 217) 17address bits

9.1.6 ROM Applications In many phone connections, your voice is purposely attennated by a few decibels to make things work better (page. 729)

3. Static RAM • 9.3.1 Static-RAM Inputs and Outputs

9.3.1 Static-RAM Inputs and Outputs D-latch when SEL = Ø OUT <- Q when SEL = WR = Ø D <- IN

4. Dynamic RAM • 9.4.1 Dynamic-RAM Structure To store 1, word = bit = 1 To store Ø, word 1, bit = Ø Bit line prechanged between H&1 To read, word = H If cell = 1 Bit line = 1 If cell = Ø, bit line = Ø