Device-Level Toolset for Interoperable Reconfigurable and Modular Design

10 likes | 133 Vues

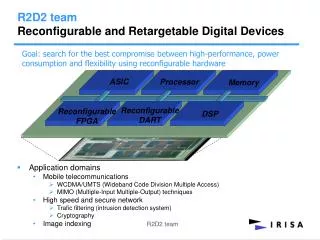

The RECINTO project addresses the need for a robust toolset for designing dynamic and partially reconfigurable systems on FPGAs. By providing device-level tools, it enables the design of modular reconfigurable systems with a focus on interoperability. The tools facilitate a streamlined design flow using Xilinx Design Language (XDL), overcoming the limitations of current commercial products. RECINTO enhances productivity by automating modifications, managing area constraints, and ensuring effective communication between design modules. Applications include secure designs and scalable architectures for video processing.

Device-Level Toolset for Interoperable Reconfigurable and Modular Design

E N D

Presentation Transcript

A device-level Toolset for InteroperableReconfigurable and Modular Design ncd Static Area Reconfigurable Area A. Otero Static Design Static Design Xilinx .bit .ncd To block Out Dynamically reconfigurable systems based on commercial FPGAs have gained research interest in the academia during the last years. Those systems can be regarded as a trade-off solution between software flexibility and hardware performance. However, the main restriction limiting its industrial exploitation is the lack of appropriate commercial tools supporting this design flow. In RECINTO (Reconfiguración Interoperable) project, a set of device-level tools have been developed to fulfill this gap. Conflicts Reconfigurable Area Static Area RECONFIGURABLE MODULES To block Out • Dynamic and Partial Reconfigurable Systems Design Flow xdl Xilinx .bit Xilinx .ncd Xilinx .bit Xilinx .ncd • Up-to-now… • Modular Design is required Xilinx .bit .ncd Make Project sponsored by Block Block RECONFIGURABLE MODULE 1 • Routing Area Constraints • Effective communications between modules • Independent design of • modules and system • Time-consuming design process • Hand-made netlists modifications required • Bus-Macros and area over-dimensioning limit designs • Incompatibility between FPGAs families Block Block BM Logic User Logic Block Block Bus-Macros RECINTO Project XDL (Xilinx Design Language) Manual modifications with FPGA editor Netlist Bitstream RECONFIGURABLE MODULE 2 • Design Interoperability ncd bit DESIGN ONCE Wrong Wiress BITGEN User Logic Increases Design Productivity What is RECINTO ToolSet? Recinto project provides a low-level toolset to design Modular Reconfigurable Systems XILINX-XDB 0.1 STUB 0.1 ASCIIXILINX-XDM V1.6###6116:XlxV32DM 3fff 17cceNrtWulz3DaW/1f6gz7MzEYywQM8sE6lCVJSl/tyd8uWZyvL4qn0rKRW1HKUKVn7t+/DRfBoKlbWnqqt2oolPPzeBTwA74FQjkyUP2FyNI83iSFb5MoWK8JVhKcIX8qaEjANRShts2ZZUla1tmwdKeAoFUepOJYibEUoh2pMWDnEShubUsRFBjlalb9t99vdbTBCJ/boKCVH29uH8v42vTYy8pfrXZ5e/3VknFigLXtB9nmfFOV9mf+SJl4yQ1mHs8/L26IEK5yLWtz7cl8+mOQYwY9lkeP8JiPHV9e7LL1OdncPPjkG9/uHf16Xeanp0XZfjo7vRr/nzm/XvyNkPBxXFUIWPrZGx4+j4+vd1TZn+qNdVY2Od9ejX7ZXv4yOH0ZodHxfXm33MKWk+Hx3vc3TB5itkNN+Rf9GtvnNKL0v09Hx9l4Ad7K9zmV/91hKaDcqr8sbmG1yk96d3OaF6p/cXmn6Lq9GMNvtPfy6zlOiRwzADfu1u8ZE2IXO3T1yyMGBQ9gebNCHSbeDU89ZTmJwVHl7VLZBTk7ewD+2Ojdpfr9LvDedFT65vcm7qx4g0/ddB/ueZ3uDJlpboWGmhdemfGTZA6b4vqkN8J5Wc0ryJrw4PaOb1TS5ND7Bzn0zWYTJJfqEkJ/WHctXDPOTabuNjmOAifV0QuPk0jE/IcNr961O30aNvgVezHbfstr9lrzTse909J2OvtPRx6CPO3230/fafeQVzb7fZLsgjtr91nCgbzb5fse8z+QtAjmC/XIQQRVByP0BrP7AW+QLwJSAyQEbAWD+wFsL2wAEhkWsE8R+mTZx/cBAZGySMeSKsQk/FvzY8OPAD4bcNaabi/E0Ga/i8dlqcbG0yXh2cQnM9xlhYMLRNQCXiIQmCcFQCIZCMBSCoRAMhdgiYTwFa+HsbJWMN5vVJLzYxGti+j1odb5INqvxfD2J55vkfBKvxit6/uktwWZPlkdnmoD0Wfy2uTIoaK2LEJx9haANPtj0wvcwMtjtfMuzgV9MplGyGa/O4g0bD0hc5iQsr/csb4/s0azkvYDJJ+yX7LPNP5kDUOn+4mIDQK6B5TiCFM67ckpjZ3qx6WIYsKoNnZ52hMIDimFfMewp0gOKtK9Ie4rRAcWorxiBIqEmobBBKGwQChuEwgahsEEo22l0HCUfJvHH5EO8Wk8Wc4Bji9AJI94BMX1nEwqL4xO6mM0mm00c2YxcpvB7vYHFCacxQy42oPHeJRS… • Low-level: deals with components and nets • Uses XDL (Xilinx Design Language), a human readable version of the ncdnetlist • Tools carry out automatic modifications of the XDL before generating the bitstream • FPGA architecture description, design parser and data structures from Rapidsmith(Brigham Young University) • As easy as… bit RECINTO Tools applies here! Architecture DB “Human readable”!! User Design Tools Xilinx doesn’t give tools for XDL (but is useful) RECINTO Tools Description Module Connector • Communications between Modules without Bus-macros • Virtual Wires (VW) to guarantee that the same nets use the equivalent resources at both sides. Lightning Reconfigurable Module Recinto Router BM BM PORT_15_CLB_X33Y28 PORT_24_CLB_X32Y28 • Graphical user interface (GUI). • Locate every resource in a FPGA. • Show up conflicts. • Move, modify or erase every module in the design Routing with area constraints! Virtual Wire • VW information can be obtained in any border in the system and applied in any compatible module. • Insert area constraints. • Resource constraints. • Smart detection of conflicts CONCLUSIONS • RECINTO ToolSet is being applied several projects in CEI: • Secure designs with Dynamic Side Channel Attack Protection • Scalable Architectures for Video Applications • Fine-grain Evolvable Hardware Architectures RECINTO Design Flow Recinto Tool-Chain System Description (XML) VW Information • Some new tools will be developed in the future: Shrinker, Modular Placer… VW information