Acceleration

This guide delves into the principles of CPU acceleration, focusing on improving processing speed through various design strategies, including single-cycle and multi-cycle architectures. It breaks down essential concepts such as the number of instructions (Nq), cycles per instruction (CPI), and the impact of cycle time on performance. With detailed explanations of pipeline design, stages (IM, DE, EX, DM, WB), and critical path optimization, it provides insights for enhancing throughput while managing associated costs. Discover effective methods for achieving greater efficiency and performance in CPU design.

Acceleration

E N D

Presentation Transcript

Acceleration • How to improve speed? • At what costs?

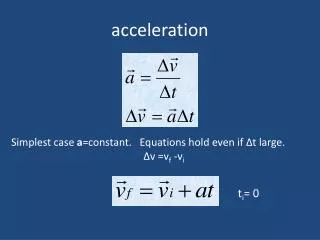

T=Nq * CPI * Cycletime • Nq, Number of instructions • CPI, Cycles Per Instruction • Cycletime

Single Cycle Design • CPI = 1 • Cycletime = Long (Longest path)

Multiple Cycle • 1 < CPI < S • Cycletime = Factor 1/S

Pipelined design • CPI = 1, (Constant) • Cycletime = Factor 1/S

“THROUGHPUT” • The total amount of work done in a given time

INSTRUCTION MEMORY STAGE (IM) Zeroext. Branch logic 0 A ALU 4 B + 31 + Sgn/Ze extend INSTRUCTION MEMORY

INSTRUCTION DECODE STAGE (DE) Zeroext. Branch logic 0 A ALU 4 B + 31 + Sgn/Ze extend

INSTRUCTION EXECUTE STAGE (EX) Zeroext. Branch logic 0 A ALU 4 B + 31 + Sgn/Ze extend

DATA MEMORY STAGE (DM) Zeroext. Branch logic 0 A ALU 4 B + 31 + Sgn/Ze extend DATA MEMORY

WRITEBACK STAGE (WB) Zeroext. Branch logic 0 A ALU 4 B + 31 + Sgn/Ze extend

Pipeline • 5 stages, (IM, DE, EX, DM, WB) • Writeback NOT in critical path • Cut critical path by 4

WRITEBACK STAGE (WB) Zeroext. CAN READ/WRITE THE SAME REG! Branch logic 0 A ALU 4 B + 31 + Sgn/Ze extend

Single Cycle Reg IM DM Reg Reg IM DM Reg

Single Cycle Reg IM DM Reg Reg IM DM Reg

4 Stage Pipe Reg IM DM Reg Reg IM DM Reg Reg IM DM Reg Reg IM DM Reg

A Program 0x30 sub $6 $0 $1 0x34 add $7 $0 $1 0x38 ori $2 $0 0xABCD 0x3C sw $5 4($0) $1 holds value 0x05

4 Stage Pipe Reg • 0x30 sub $6 $0 $1 IM DM Reg • 0x34 add $7 $0 $1 Reg IM DM Reg • 0x38 ori $2 $0 0xABCD Reg IM DM Reg • 0x3C sw $5 4($0) Reg IM DM Reg

Step 1 Reg • 0x30 sub $6 $0 $1 IM DM Reg • 0x34 add $7 $0 $1 Reg IM DM Reg • 0x38 ori $2 $0 0xABCD Reg IM DM Reg • 0x3C sw $5 4($0) Reg IM DM Reg

Step 2 Reg • 0x30 sub $6 $0 $1 IM DM Reg • 0x34 add $7 $0 $1 Reg IM DM Reg • 0x38 ori $2 $0 0xABCD Reg IM DM Reg • 0x3C sw $5 4($0) Reg IM DM Reg

Step 3 Reg • 0x30 sub $6 $0 $1 IM DM Reg • 0x34 add $7 $0 $1 Reg IM DM Reg • 0x38 ori $2 $0 0xABCD Reg IM DM Reg • 0x3C sw $5 4($0) Reg IM DM Reg

Step 4 Reg • 0x30 sub $6 $0 $1 IM DM Reg • 0x34 add $7 $0 $1 Reg IM DM Reg • 0x38 ori $2 $0 0xABCD Reg IM DM Reg • 0x3C sw $5 4($0) Reg IM DM Reg

Step 5 Reg • 0x30 sub $6 $0 $1 IM DM Reg • 0x34 add $7 $0 $1 Reg IM DM Reg • 0x38 ori $2 $0 0xABCD Reg IM DM Reg • 0x3C sw $5 4($0) Reg IM DM Reg

Zeroext. Branch logic 0 A ALU 4 B + 31 + Sgn/Ze extend • > 0x30 sub $6 $0 $1 • 0x34 add $7 $0 $1 • 0x38 ori $2 $0 0xABCD • 0x3C sw $5 4($0)

Zeroext. Branch logic 0 A ALU 4 B + 31 + Sgn/Ze extend • 0x30 sub $6 $0 $1 • > 0x34 add $7 $0 $1 • 0x38 ori $2 $0 0xABCD • 0x3C sw $5 4($0)

Zeroext. Branch logic 0 A ALU 4 B + 31 + Sgn/Ze extend • 0x30 sub $6 $0 $1 • 0x34 add $7 $0 $1 • > 0x38 ori $2 $0 0xABCD • 0x3C sw $5 4($0)

Zeroext. Branch logic 0 A ALU 4 B + 31 + Sgn/Ze extend • 0x30 sub $6 $0 $1 • 0x34 add $7 $0 $1 • 0x38 ori $2 $0 0xABCD • > 0x3C sw $5 4($0)