High-Throughput Wireless Architecture for Energy-Efficient Signaling

10 likes | 113 Vues

This project focuses on a wireless architecture with high throughput, low complexity, and energy efficiency. The goal is to develop energy-efficient constellation signaling with low decoding complexity while exploring channel fading mechanisms. The study involves investigating optimal constellation matching and the impact of analog impairment on the proposed constellation. Work is in progress using an FPGA-based Test Bed to simulate system performance and evaluate constellation efficiency.

High-Throughput Wireless Architecture for Energy-Efficient Signaling

E N D

Presentation Transcript

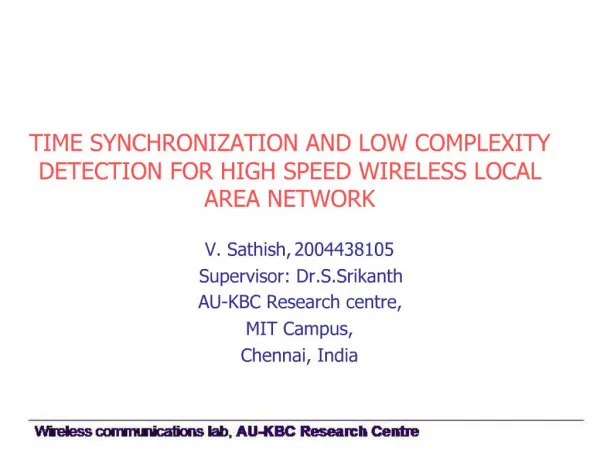

Digital Up Converter Digital to Analog Converter Transmitter Front-End Symbols IFFT, Add CP Computer Packet Detection Timing Recovery, Remove CP, FFT Digital Down Converter Analog to Digital Converter Receiver Front-End Symbols Analog Impairment FPGA Low Complexity, High throughput wireless architecture Dayu Huang Advisor: Prof. Sean Meyn, Prof. Ada S.Y. Poon Illinois Center for Wireless Systems GOAL PROPOSED METHODOLOGY • Wireless Architecture • High Throughput • Low Complexity • Energy Efficient • Signaling with energy efficient constellation which is also of low decoding complexity. • Exploring channel fading mechanism. ISSUES • Optimal Constellation matching to channel statistic leads to simple suboptimal constellation that outperforms in throughput conventional QAM of the same decoding complexity, as indicated by the capacity plot. • Capacity plot implies ideal case; Study with simulation of system with proposed constellation is in progress, using more realistic channel model. • Impacts of Analog Impairment on proposed constellation will be investigated by experiment with a FPGA-based Test Bed. • Constellation on the right has the same decoding complexity as 16QAM, but considerably outperforms 64QAM (left) at high SNR. WORK IN PROGRESS • FPGA-based Test Bed • the system diagram of the test bed