Space vs. Speed: Binary Adders

This document explores the trade-off between space and speed in the design of binary adders using VHDL. It covers key concepts including the 4-bit Ripple Carry Adder and Carry Lookahead Adder, highlighting their designs and performance metrics. The Ripple Carry Adder's longest delay path and its comparison with Carry Lookahead techniques illustrate the impact of architecture on speed, while assessing gate delays in 16-bit and 64-bit adders. By examining the concepts of propagation and generation in adders, this guide illustrates efficient design practices in digital circuits.

Space vs. Speed: Binary Adders

E N D

Presentation Transcript

Space vs. Speed: Binary Adders 11.3 Space vs. Speed

Binary Adders • VHDL Adder • Carry Lookahead Adder

4-Bit Adder C 1 1 1 0 A 0 1 0 1 B0 1 1 1 S 1 1 0 0

Adder in VHDL entity adder is port ( a: in STD_LOGIC_VECTOR (3 downto 0); b: in STD_LOGIC_VECTOR (3 downto 0); sum: out STD_LOGIC_VECTOR (3 downto 0); carry: out STD_LOGIC ); end adder;

AiBi 00 01 11 10 Ci 0 1 1 1 1 1 Ci+1 Ci+1 = Ai & Bi # Ci & Bi # Ci & Ai

Binary Multiplier 2 bit by 2 bit Half Adders are Sufficient Since there is no Carry-in in addition to the two inputs to sum

Binary Multiplier 4 bit by 3 bit 4 bit by 3 bit yields 7 bit result

Binary Adders • VHLD Adder • Carry Lookahead Adder

Carry Lookahead Adder C2 = G1 + P1(G0 + P0C0) = G1 + P1G0 + P1P0C0 C3 = G2 + P2(G1 + P1 (G0 + P0C0)) = G2 + P2(G1 + P1 G0 + P0C0) = G2 + P2G1 + P2P1G0 + P2PlP0C0 G0-3 = G3 + P3G2 + P3P2G1 + P3P2PlG0 P0-3 = P3P2PlP0

Typically, longest delay path through n-bit ripple carry adder is 2n + 2 • Tends to be one of the largest delays in a typical computer design Counts as 2 gate delays 0 2 2 4 0 1 3 4 1 0

4 4 0 2 6 0 5 6 4

4 6 6 4 0 2 8 0 7 8 6

8 4 6 8 6 4 0 2 10 0 9 10 8

8 10 4 6 10 8 6 4 • 10 Gate Delays • 16-bit Adder -- 34 Gate Delays • 64-bit Adder -- 130 Gate Delays

Carry Lookahead Adder • Uses Propogate and Generate signals to “lookahead” for incoming carry signals • More complicated hardware configuration • Substantial decrease in gate delays

Ripple Carry PFA: Partial Full Adders Carry Lookahead

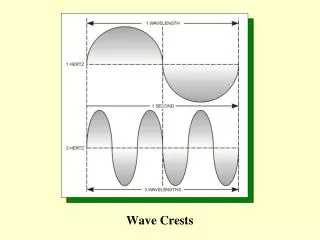

Propagate P = A xor B If P = ‘1’ then the carry is “propagated” through. If P = ‘0’ then the carry is not “propagated” through. • Generate G = A and B • If G = ‘1’ a carry is “generated” regardless • of the carry bit.

Cin A B P G Cout S 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 0 0 0 1 0 1 1 0 0 1 1 0 1 0 1 1 0 0 1 0 1 0 0 1 0 0 1 0 1 0 0 1 For final carry determination, the Propagate signal is ANDed with the Carry Outand the Generate signal is ORed to the resulting signal. G P Cin Cout

Cin A B Cin A B P G P G Cout S Cout S 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 0 0 0 1 0 1 1 0 0 1 1 0 1 0 1 1 0 0 0 1 0 1 1 0 0 1 1 0 1 0 1 1 0 0 1 0 1 0 0 1 0 0 1 0 1 0 0 1 0 0 1 0 1 0 0 1 0 0 1 0 1 0 0 1 Always Generate a Carry forA = 1, B = 0 Propagate the Carry in

2 4 1 2 4 3 Cout

2 4 PFA For Bit # 1 1 2 4 1 3 4 2 2 3 2 3 1 4 2 1 2 Cout 3 2 3 1 4 2

Bit #1 Bit #2 2 2 4 6 1 1 4 Bit #3 Bit #4 2 2 6 6 1 4 4

Significant Delay Reduction • 4 - bit Ripple: 10 Delays CLA: 6 Delays 1 CLA level: 1*4 + 2 = 6 • 16 - bit Ripple: 34 Delays CLA: 10 Delays 2 CLA levels: 2*4 + 2 = 10 • 64 - bit Ripple: 130 Delays CLA: 14 Delays 3 CLA levels: 3*4 + 2 = 14 But at the expense of a significant increase in the number of gatesused by the circuit