Stavelet Update

This update provides detailed insights into the latest developments in Stavelet technology, focusing on numerology, shield optimization, and bias voltage analysis. It discusses the impact of configurations on noise levels, especially on the SP+ line, and outlines future programming goals. Key considerations include removing AC coupled shields to mitigate issues, strategies for reducing noise spikes correlated with ADC readout, and enhancing the performance through revised shielding techniques. Upcoming plans target further optimizations and noise reduction strategies for improving overall system integrity.

Stavelet Update

E N D

Presentation Transcript

Stavelet Update 10.12.2010 Peter W Phillips

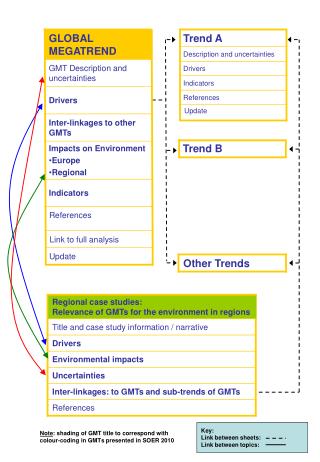

Contents • Stavelet Numerology and Dead Chip • Shield Configurations • Bias Voltage • Noise on SP+ line • Future Programme

1. Stavelet Numerology The Stavelet Dead Chip

Dead Chip: A Victim of Violent Crime Certainly not infant mortality!

2. Shield Optimisation: intention For DC coupled hybrids, make the DC shield connection represented by the black line. Initially retain AC shield connections at the other side of all hybrids, then start taking them off.

Shield Optimisation: reality PB DC DC DC DC DC DC DC • Conditions for A-F: • New IF board • EoS linear 3V3 • HSIO switch mode 48V PSU • XIlinx cable plugged in • ADCs not being read • Screened SP cable • TTi TSX3510 @5A CI Note: configuration “B” was a mistake. I meant to remove the AC coupled shield link from hybrid 7, not hybrid 6… AC AC AC AC AC DC DC DC DC DC AC AC AC AC AC AC AC AC AC AC DC DC DC DC DC AC AC AC AC AC DC DC DC DC DC LIN LIN LIN LIN LIN D A AC DC AC AC DC AC DC E B LIN LIN AC DC AC AC DC AC DC F C LIN (PB – previous best)

ENC for various shield configurations ENC (PB – previous best) 00 01 10 11 20 21 30 31 40 41 50 51 60 61 70 71 Hybrid / Column It’s obvious that removing the AC coupled shield bonds from hybrid 6 at step B was a bad idea. Otherwise we got better in some places, worse in others…

Stavelet ENC @2fC, TSX3510P@5A 1330-3, 150V bias, linear EoS 3V3 DC SWAPPED DEAD CHIP AC DC AC AC DC AC DC F LIN

Stavelet ENC @2fC, TSX3510P@5A PREVIOUS BEST(1284-6) shield pads separated, EoS linear PB DC AC DC AC AC DC AC DC LIN DEAD CHIP

3.Bias Voltage • Using TTi Supply @5.0A • Strobe Delay set at 150V • Measure ENC for 100 to 260V in 20V steps • Conditions for HV study: • New IF board • EoS linear 3V3 • HSIO switch mode 48V PSU • XIlinx cable plugged in • ADCs not being read • UNSCREENED SP cable • TTi TSX3510 @5A CI

ENC as f(Vdet) ENC Column

ENC as f(Vdet) ENC ENC V V ENC ENC V V

Stavelet ENC @2fC, Tti @ 5A 1341-6, 150V bias, linear EoS 3V3, one choke on SP- only 150V DC SWAPPED DEAD CHIP AC DC AC AC DC AC DC F LIN

Stavelet ENC @2fC, Tti @ 5A 1341-3, 200V bias, linear EoS 3V3, one choke on SP- only 200V DC SWAPPED DEAD CHIP AC DC AC AC DC AC DC F LIN

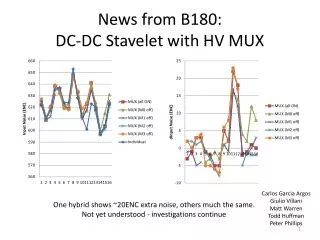

4. Noise on power lines • At upgrade week I reported ~1.5V spikes (left) • Correlated with ADC readout activity. These are I2C devices (single ended) so not such a big surprise. • Matt changed the firmware to read ADCs on demand • I changed the software to remove said demand. • Sadly this did not reduce the stavelet noise • Now look to see what’s left… Single Ended Probe on SP+ 1.81V Pk-Pk!!! Correlated with EoS ADC (I2C) traffic

Noise on SP+ Jan Stastny CS at 5A, one choke TTi TSX 3510 at 5.0A CI, one choke With TTi unit, trace is similar at all times. With repaired JS current source, there is more voltage noise during readout (above). Between bursts, the noise band is ~1/3 of that shown.

Noise on SP+ • Addition of a second CM choke (with 2 turns) gives a considerable reduction in both the baseline noise and spike amplitude. • Noise levels during and between bursts is now similar. • ENC plot overleaf Jan Stastny CS at 5A, two chokes

Stavelet ENC @2fC, repaired CS@5A 1333-27, 200V bias, linear EoS 3V3, two chokes 200V DC SWAPPED DEAD CHIP AC DC AC AC DC AC DC F LIN

Noise on SP+ IN OUT Jan Stastny CS at 5A + SCTLV filter Adding a more complex filter (PP3 prototype) introduces a phase lag to the current measurements, which disturbs the control loop. Oscillation is the result .

5. Future Programme • Further shield configurations • Replace fused bias bonds • Float LVDS screen • Revert to previous best or common shield and try higher Vdet • Extra noise at“GND” end of stavelet (H0) • Add C between SP+ and SP1 at EoS • Longer cables and/or chokes CM between IF and EoS • Split ground planes at EoS (again) • Current Source • Try screened SP cable with JS unit • Try remote sensing • Revised unit due soon • Updated HSIO firmware & software (presently being debugged) • Fibre optic ethernet • Ability to pulse noise injection lines • Double trigger noise tests • SP Plugin boards