Design Technology Committee

Design Technology Committee. Bill Read Chairman DTC August 20, 2012. Design Technology Committee. DTC was (re-)formed under the IEEE Council on EDA (CEDA) in 2010 Mission: Act as the voice of the EDA customers to

Design Technology Committee

E N D

Presentation Transcript

Design Technology Committee Bill Read Chairman DTC August 20, 2012

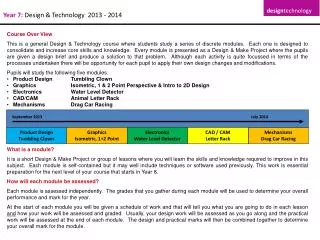

Design Technology Committee • DTC was (re-)formed under the IEEE Council on EDA (CEDA) in 2010 • Mission: Act as the voice of the EDA customers to • Promote strategic solutions through the identification of gaps between projected EDA capabilities and the future needs of the semiconductor and system design community. • Promote interoperability of EDA toolsand best practice sharing.

2011-2012 Focus • Vender Gap Analysis • Identify a common set of gaps and requirements gaps between projected EDA capabilities and the future needs of the semiconductor and system design communities • Prioritized gaps in Digital Implementation (RTL-to-GDS) and Verification

Digital Implementation Areas • Power and Power Grid Analysis/IR Drop Analysis • Clock Tree Synthesis / Insertion • Physical Synthesis and Optimization • Power Optimization • Routing • ECO • Static Timing Analysis • Signal Integrity Analysis • Floorplanning • Aging Analysis and ESD/EMI Analysis • Chip Finishing

Digital Implementation Gaps • Need for more interconnect aware implementation throughout the flow • Need better correlation between early estimates, sign-off results, and silicon • Need for better awareness of process variability and of power throughout the flow • Need to consider more physical effects earlier in the flow for better convergence • Need improvements of runtime, capacity, and better scalability to larger designs

Functional Verification Areas • Formal Verification • Coverage Analysis • Emulation • Verification IP • Post-silicon Validation

Functional Verification Gaps • Performance • Faster runtimes of the tools/ algorithms • Support of multi-core architectures • Better scalability of multi-threading • Capacity • Ability to handle increasing complexity of designs, e.g. full chip, mixed-signal designs • Full support of mixed methodological approaches, e.g. formal and simulation • Quality of results • Standards and standards compliance • New standards needed, e.g. coverage database • Full compliance and same interpretation of available standards required

2011-2012 Results • Vender Gap Analysis • Identified and prioritized gaps and requirements • Reviewed the results with EDA vendors as a group and in individual meetings • Information was useful to EDA vendors, but too near-term to effect their current roadmaps • Vendor 12-18 month roadmaps are dominated by current development and user requests

2012-2013 Focus • 2-5 year needs the semiconductor and system design communities to effect EDA vendor long-term roadmaps • EDA tool roadmap needs that complement the ITRS

2012-2013 Focus • Scalability of tools required for each node • Size of partitions that should be processed in reasonable time • Turnaround time expectations for key functions • Quality of results requirements • Methodology improvements for complexity, performance, power, etc. • Recommendations on limiting options within tools to improve QOR, performance, etc. • New Functionality requirements • Capabilities required for new technology nodes • Capabilities required for heterogeneous designs • Capabilities required for 3D die design and die-package codesign • Provide benchmark designs for use by EDA vendors