Functional Vector Generation for HDL Models Using Linear Programming and 3-Satisfiability

This research explores a novel hybrid approach that integrates linear programming and the 3-Satisfiability (3-SAT) technique for generating functional test vectors in Hardware Description Language (HDL) models. The methodology employs Boolean and word-level operators to model interconnections and establish constraints for module inputs and outputs. Coverage-directed simulations are utilized to enhance testing efficiency, focusing on achieving desired metrics such as path coverage. The study presents results from initial tests, ongoing work, and future directions to improve verification processes in digital design.

Functional Vector Generation for HDL Models Using Linear Programming and 3-Satisfiability

E N D

Presentation Transcript

Functional Vector Generation for HDL Models Using Linear Programming and 3-Satisfiability Farzan FallahSrinivas Devadas Laboratory for Computer Science MIT Kurt Keutzer Department of EECS UC Berkeley

Outline • Introduction • Functional test vector generation strategy • New hybrid SAT method • Results • Ongoing work

Introduction Design Verification if (C) A = 1; else A = 2; $display(“%d”, A);

Introduction Design Verification • How do we solve the design verification problem? • Formal verification • Who specifies correctness property? • Simulation • How do you get the test vectors?

Introduction Coverage Directed Simulation • Choose a coverage metric, e.g., line/branch/path coverage. • Automatically generate vectors that achieve targeted coverage under chosen metric.

W > Z Functional Vector Generation Strategy • We view HDL descriptions as interconnections of combinational modules which include Boolean and word-level operators. f X + Y c G x2 0 d 1 x0

Functional Vector Generation Strategy • Boolean operators: AND, OR, and INVERTER gates. • Word-level operators: Comparison: Addition/Subtraction: Increment/Decrement: Scalar multiplication: Left/Right shift:

Functional Vector Generation Strategy • Any other operator must be converted into a collection of the previous operators. Example can be modeled as,

Functional Vector Generation Strategy • can be modeled as, and 4 constraints over Y and individual bits of X for each pi , where piis a partial product. Z = 2n-1pn-1+ 2n-2pn-2+ … + p0

Functional Vector Generation Strategy • We choose path coverage metric. • A path is a set of alternating modules and signals. S1 S2 S3 m1 m2 P={S1, m1, S2, m2, S3}

Functional Vector Generation Strategy • Sensitizing a sub-path through a module means the value of the input to the path should affect the value at the output. A 0 0 • Sensitizing a path means sensitizing each module .

AND 1 Functional Vector Generation Strategy • Sensitization of a sub-path through a module will require values at some of the module inputs. • Value of side-inputs for logic gates, OR 0 Side-inputs

Value of side-input for word-level operators (assuming unsigned numbers), A > C C A A B k B Functional Vector Generation Strategy C

Functional Vector Generation Strategy b X > c Y a Constraints: b = 1 c = a AND b b = X > Y • Find a solution that satisfies the set of constraints. • Write module input-output relationship for every module in the circuit. • Write sensitization requirement on intermediate signals. • Select a path.

Functional Vector Generation Strategy • How do we find a solution to the constraints? • Use Boolean clauses to modelall modules and solve resulting 3-SAT problem. • Use Boolean clauses andlinear constraints to model modules and solve the problem using 3-SAT solver andinteger programsolver. • Both methods use Branch and Bound technique.

X Z Y X Y 3-SAT Approach • Use Boolean clauses to model input-output relationship of each gate.

3-SAT Approach • Solve the resulting 3-SAT problem to find a satisfying assignment for all input variables. • 3-SAT approach is not efficient because word-level operators have to be modeled using Boolean operators.

x2 x2 0 0 d d 1 1 x0 x0 c c X W + > Y Z e e a a b b New Hybrid Satisfiability Approach 1 1 0 0 f f g g G h h • We want to exercise a path in the circuit. • Use linear word-level operators (Linear arithmetic constraints, LACs) to model data-path.

x2 1 0 d 1 x0 0 c f g h e a b New Hybrid Satisfiability Approach • Choose values for side-inputs.

x2 0 d 1 x0 c e a b New Hybrid Satisfiability Approach 1 0 f g h • Control part is modeled using Boolean operations. ?? • Choose values for side-inputs. • Gates are modeled using Boolean clauses.

New Hybrid Satisfiability Approach Correlation: x0 is first bit of X x2 is third bit of X g is equal to G • Gates are modeled using Boolean clauses. • There is correlation between Boolean variables and integer variables.

Simplifying SAT New Hybrid Satisfiability Approach Correlation: x0 is first bit of X x2 is third bit of X g is equal to G • Essential variable: If there is a single variable in TRUE (complemented) form in a clause it must be set to 1(0). • c must be set to 0.

Simplifying SAT New Hybrid Satisfiability Approach Correlation:x0-X, x2-X, g-G Current assignment: c=0, e=1 • New essential variables might be created.

Simplifying SAT New Hybrid Satisfiability Approach Correlation:x0-X, x2-X, g-G Current assignment: c=0, e=1 , b=1 • Unate variable: If a variable only appears in true (complemented) form it can be set to 1(0). • Note that there was no integer variable correlated to b. • Use unate variable rule recursively. • We can set b to 1.

Linear infeasibility New Hybrid Satisfiability Approach Correlation:x0-X, x2-X, g-G Current assignment: c=0, e=1, b=1, f=0 • If SAT is infeasible, there is no solution for the constraints, otherwise we continue search for the solution. • Use polynomial time sufficiency check for SAT infeasibility. • If linear relaxation of LACs is infeasible, there is no solution to the constraints. This can be checked in polynomial time.

Branching New Hybrid Satisfiability Approach Correlation:x0-X, x2-X, g-G Current assignment: c=0, e=1, b=1, f=0 • Choose an input variable which appears in clauses most (x2). • Select a Boolean variable heuristically and set it to 1(0), if it fails to find a feasible solution, set it to 0(1). • Set x2 to 1.

Simplifying SAT New Hybrid Satisfiability Approach Correlation:x0-X, x2-X, g-G Current assignment: c=0, e=1, b=1, f=0, x2=1 • Set d to 1.

Branching New Hybrid Satisfiability Approach Correlation:x0-X, x2-X, g-G Current assignment: c=0, e=1, b=1, f=0, x2=1, d=1 , h=1 • Set h to 1. • There is a correlation between x2 and X, use new integer variables and modify LACs.

Branching New Hybrid Satisfiability Approach Correlation: x0-X, x2-X, g-G Current assignment: c=0, e=1, b=1, f=0, x2=1, d=1, h=1 • Find a solution to LACs using Integer Programming.

Branching New Hybrid Satisfiability Approach Solution Boolean Variables: c=0, e=1, b=1, f=0, x2=1, d=1, h=1, x0=X, g=X Integer Variables: X7-3=0, X1-0=0, Y=0, W=4, Z=0, G=1 • Free Boolean variables correlated to integer variables, are set to the appropriate values.

Branching New Hybrid Satisfiability Approach Solution Boolean Variables: c=0, e=1, b=1, f=0, x2=1, d=1, h=1, x0=0, g=X Integer Variables: X7-3=0, X1-0=0, Y=0, W=4, Z=0, G=1 • Free Boolean variables correlated to integer variables, are set to the appropriate values.

Branching New Hybrid Satisfiability Approach Solution Boolean Variables: c=0, e=1, b=1, f=0, x2=1, d=1, h=1, x0=0, g=1 Integer Variables: X7-3=0, X1-0=0, Y=0, W=4, Z=0, G=1 • Free Boolean variables correlated to integer variables, are set to the appropriate values.

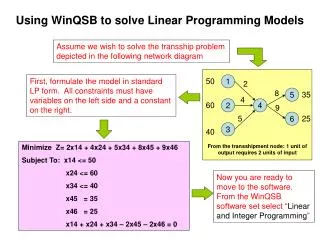

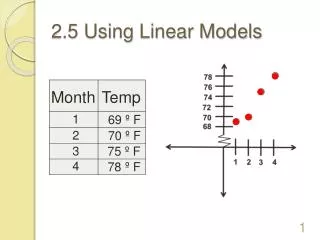

Results HSAT 3-SAT Example Exp. Time/ Sat. Time #Clauses/ #LACs #Clauses Sat. Time pport 17/18 685 <1 s 1.2/4.7 s schsm <1 s 841 141/24 3.1/261 s ctla 1355 <1 s 1/24 >1000 s ctlbc <1 s 1341 1/60 4.9/142 s 0/104 mult16 8466 16 s >1000 s

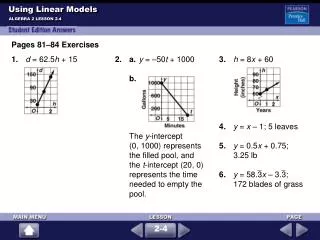

Ongoing Work • Improvement on satisfiability checking using seamless integration of linear programming and satisfiability. • Currently we use conventional time frame expansion strategy for sequential HDL models. • We are exploring more efficient algorithms. • We are working on generating functional vectors for a variety of code coverage metrics.

OCCOM talk Ongoing Work Future system overview Simulation driver (vectors) Simulation model (HDL) Simulation monitor (yes/no) Simulation engine LP-3SAT Vector Generation No OCCOM Coverage Analysis Is it enough? Diagnosis of Unverified Portions Yes Stop