Thread Level Parallelism

Thread Level Parallelism. OoO & Cie ne peuvent rien contre les défauts de cache Prefetching Multithreading au niveau du pipeline. Multithreading. Multithreading Coarse Grained MT. Masquer la latence mémoire et le swap entre deux threads. IBM STAR RS64-IV (POWER4 - 2000).

Thread Level Parallelism

E N D

Presentation Transcript

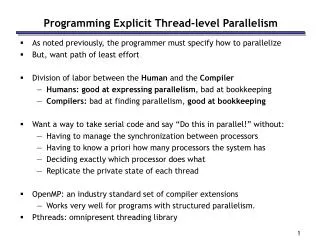

Thread LevelParallelism • OoO & Cie ne peuvent rien contre les défauts de cache • Prefetching • Multithreading au niveau du pipeline

MultithreadingCoarseGrained MT Masquer la latence mémoire et le swap entre deux threads IBM STAR RS64-IV (POWER4 - 2000)

MultithreadingFine Grained MT Masquer la latence des caches, combler les bulles HEP (1983) Tera Sun niagara

MultithreadingSimultaneousMT Combler les bulles, maximiser l’utilisation des unités superscalaires Pentium 4, Nehalem, Power5, Power6

MultithreadingCMT – FMT - SMP • Avantages • Meilleure utilisation du pipeline • Réactivité (lock) • Partage de données entre 2 threads • Régulation de charge • Inconvénients • Partage de cache perte de performance • Gestion des priorités • Difficultés de mise en œuvre des techniques de scrutation • Solution • Désactivation • Appariement de threads compatibles

Machines multiprocesseurs à mémoire partagée • SMP • Mémoire centralisée

Machines multiprocesseurs à mémoire partagée • SMP • Mémoire centralisée • NUMA • Mémoire répartie

SMP • Organisation classique: • Mémoire • Bus • Cache • Cœur • Le bus synchronise les différents cœurs. • Bus unique pas plus d’une dizaine de cœurs • Bus en étoile (avec des filtres)

SMP • Graup : le cache L2 est devant la mémoire

SMPsynchronisation de la mémoire • Une même donnée peut être à la fois : • En mémoire, • Dans un cache, dans des caches, • Dans un registre, dans des registres, • Quelle est la bonne version ? • Faire en sorte qu’il n’y ait qu’une version • Seulement aux yeux du programmeur • Donner au programmeur la même vision de la mémoire que sur une machine monoprocesseur programmée à l’aide de threads (exécutés en séquence).

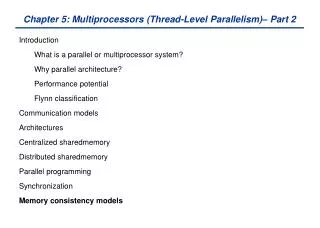

SMPsynchronisation de la mémoire • Consistance séquentielle (Lamport 1979), Sémantique de l'entrelacement : «Un multiprocesseur est séquentiellement consistant si toute exécution résulte d'un entrelacement des séquences d'instructions exécutées par les processeurs et qui préserve chacune des séquences. En particulier tous les processeurs voient les écritures dans le même ordre. » • Exemple : au départ { x = 0, y = 0} on lance 2 threads : T1 { x = 1 ;print y } T2 { y = 1; print x } On ne devrait pas voir 0 0.

SMPsynchronisation de la mémoire • Consistance séquentielle (Lamport 1979), Sémantique de l'entrelacement : «Un multiprocesseur est séquentiellement consistant si toute exécution résulte d'un entrelacement des séquences d'instructions exécutées par les processeurs et qui préserve chacune des séquences. En particulier tous les processeurs voient les écritures dans le même ordre. » • Exemple : au départ { x = 0, y = 0} on lance 2 threads : T1 { x = 1 ;print y } T2 { y = 1; print x } On ne devrait pas voir 0 0. Compilateur + OoO

SMPsynchronisation de la mémoire • Consistance séquentielle (Lamport 1979), Sémantique de l'entrelacement : «Un multiprocesseur est séquentiellement consistant si toute exécution résulte d'un entrelacement des séquences d'instructions exécutées par les processeurs et qui préserve chacune des séquences. En particulier tous les processeurs voient les écritures dans le même ordre. » • Exemple : au départ { x = 0, y = 0} on lance 2 threads : T1 { x = 1 ;print y } T2 { y = 1; print x } On ne devrait pas voir 0 0. Barrières Mémoires

Implémentation de la cohérence séquentielle Mémoire cache à 1 octet A=0 B=0 C=0

Implémentation de la cohérence séquentielle A ? A=0 B=0 C=0

Implémentation de la cohérence séquentielle A ? A ? A=0 B=0 C=0

Implémentation de la cohérence séquentielle A ? A=0 A=0 B=0 C=0

Implémentation de la cohérence séquentielle A=0 A=0 A=0 B=0 C=0

Implémentation de la cohérence séquentielle A=1 A=1 A=0 B=0 C=0

Implémentation de la cohérence séquentielle A=2 A=2 A=0 B=0 C=0

Implémentation de la cohérence séquentielle A? A=2 A=2 A=0 B=0 C=0

Implémentation de la cohérence séquentielle A? A=2 A? A=0 B=0 C=0

Implémentation de la cohérence séquentielle A? A=2 A=2 A=0 B=0 C=0

Implémentation de la cohérence séquentielle A=2 A=2 A=2 A=2 A=2 A=2 B=0 C=0

Implémentation de la cohérence séquentielle A=3 A=3 A=2 A invalide A=2 B=0 C=0

Implémentation de la cohérence séquentielle A=3 A=3 A invalide A=2 B=0 C=0

Implémentation de la cohérence séquentielle B? A=3 A=2 B=0 C=0

Implémentation de la cohérence séquentielle B? A=3, B? A=2 B=0 C=0

Implémentation de la cohérence séquentielle B? B=0 A=3 B=0 C=0

Implémentation de la cohérence séquentielle B=0 B=0 B=0 A=3 B=0 C=0

Protocole ModifiedSharedInvalid(MSI) Pr Wr M Pr Wr / Invalid Bus Read / Flush Bus ReadX / Flush S Pr Wr / Bus ReadX Bus ReadX / Flush Pr Rd / Bus Read I

Implémentation de la cohérence séquentielle Pr Wr M PrRD A Pr Wr / Invalid Bus Read / Flush Bus ReadX / Flush S Pr Wr / Bus ReadX Bus ReadX / Flush Pr Rd / Bus Read A=0 B=0 C=0 I

Implémentation de la cohérence séquentielle Pr Wr M PrRD A Pr Wr / Invalid Bus Read / Flush Bus ReadX / Flush S Pr Wr / Bus ReadX BusRD A Bus ReadX / Flush Pr Rd / Bus Read A=0 B=0 C=0 I

Implémentation de la cohérence séquentielle Pr Wr M PrRD A Pr Wr / Invalid Bus Read / Flush Bus ReadX / Flush S Pr Wr / Bus ReadX A=0 Bus ReadX / Flush Pr Rd / Bus Read A=0 B=0 C=0 I

Implémentation de la cohérence séquentielle Pr Wr M A=0 A=0 Pr Wr / Invalid Bus Read / Flush Bus ReadX / Flush S Pr Wr / Bus ReadX Bus ReadX / Flush Pr Rd / Bus Read A=0 B=0 C=0 I

Implémentation de la cohérence séquentielle Pr Wr M A=1, PrWr A A=0 Pr Wr / Invalid Bus Read / Flush Bus ReadX / Flush S Pr Wr / Bus ReadX Bus ReadX / Flush INVALID A Pr Rd / Bus Read A=0 B=0 C=0 I

Implémentation de la cohérence séquentielle Pr Wr M A=1, PrWr A=1 Pr Wr / Invalid Bus Read / Flush Bus ReadX / Flush S Pr Wr / Bus ReadX Bus ReadX / Flush Pr Rd / Bus Read A=0 B=0 C=0 I

Implémentation de la cohérence séquentielle Pr Wr M A=2 A=2 Pr Wr / Invalid Bus Read / Flush Bus ReadX / Flush S Pr Wr / Bus ReadX Bus ReadX / Flush Pr Rd / Bus Read A=0 B=0 C=0 I

Implémentation de la cohérence séquentielle Pr Wr M PrRd A A=2 A=2 Pr Wr / Invalid Bus Read / Flush Bus ReadX / Flush S Pr Wr / Bus ReadX Bus ReadX / Flush Pr Rd / Bus Read A=0 B=0 C=0 I

Implémentation de la cohérence séquentielle Pr Wr M PrRd A A=2 Pr Wr / Invalid Bus Read / Flush Bus ReadX / Flush S Pr Wr / Bus ReadX BusRd A Bus ReadX / Flush Pr Rd / Bus Read A=0 B=0 C=0 I

Implémentation de la cohérence séquentielle Pr Wr M A? A=2 Pr Wr / Invalid Bus Read / Flush Flush Bus ReadX / Flush S Pr Wr / Bus ReadX A=2 Bus ReadX / Flush Pr Rd / Bus Read A=0 B=0 C=0 I

Implémentation de la cohérence séquentielle Pr Wr M A=2 A=2 A=2 Pr Wr / Invalid Bus Read / Flush Bus ReadX / Flush S Pr Wr / Bus ReadX A=2 Bus ReadX / Flush A=2 Pr Rd / Bus Read A=2 B=0 C=0 I

Implémentation de la cohérence séquentielle Pr Wr M A=3, PrWr A=2 A=2 Pr Wr / Invalid Bus Read / Flush Bus ReadX / Flush S Pr Wr / Bus ReadX INVALID A Bus ReadX / Flush Pr Rd / Bus Read A=2 B=0 C=0 I

Implémentation de la cohérence séquentielle Pr Wr M A=3 A=3 A=2 Pr Wr / Invalid Bus Read / Flush Bus ReadX / Flush S Pr Wr / Bus ReadX Bus ReadX / Flush Pr Rd / Bus Read A=2 B=0 C=0 I

Implémentation de la cohérence séquentielle Pr Wr M PrRd B A=3 A=2 Pr Wr / Invalid Bus Read / Flush Bus ReadX / Flush S Pr Wr / Bus ReadX Bus ReadX / Flush Pr Rd / Bus Read A=2 B=0 C=0 I

Implémentation de la cohérence séquentielle Pr Wr M PrRd B A=3 Pr Wr / Invalid Flush A Bus Read / Flush Bus ReadX / Flush S Pr Wr / Bus ReadX A=3, BusRd B Bus ReadX / Flush Pr Rd / Bus Read A=2 B=0 C=0 I

Implémentation de la cohérence séquentielle Pr Wr M PrRd B Pr Wr / Invalid Bus Read / Flush Bus ReadX / Flush S Pr Wr / Bus ReadX B=0 Bus ReadX / Flush Pr Rd / Bus Read A=3 B=0 C=0 I

Implémentation de la cohérence séquentielle Pr Wr M B=0 B=0 Pr Wr / Invalid Bus Read / Flush Bus ReadX / Flush S Pr Wr / Bus ReadX Bus ReadX / Flush Pr Rd / Bus Read A=3 B=0 C=0 I

Optimisation MSI Pr Wr M A=1, PrWr A A=0 Pr Wr / Invalid Bus Read / Flush Bus ReadX / Flush S Pr Wr / Bus ReadX Bus ReadX / Flush INVALID A Pr Rd / Bus Read A=0 B=0 C=0 I