XeON PHI

XeON PHI. Topics. What are multicore processors? Intel MIC architecture Xeon Phi Programming for Xeon Phi Performance Applications. What are multicore processors?. What are multicore processors?. What are Multicore Processors?. What are multicore processors?. Advantages:

XeON PHI

E N D

Presentation Transcript

Topics • What are multicore processors? • Intel MIC architecture • Xeon Phi • Programming for Xeon Phi • Performance • Applications

What are multicore processors? • Advantages: • I/O latency reduction – many operations are performed inside the die • Power efficiency – a dual core processor will require less power than 2 single core processors. • Area reduction – more common circuitry yields less redundancy. • Higher performance – utilizing parallel coding techniques allows for an increase in overall performance.

What are multicore processors? • Disadvantages: • Parallelization overhead – the take advantage of multiple cores an adequate OS and optimized application code is needed. • SW development difficulties – multiple cores and threads increase the difficulty of code development. • HW development difficulties – integrating multicore chips reduce production yield in comparison to the less dense single chip designs.

Intel’s MIC architecture • The Larrabee project (2006) • Originally designed for GPU purposes. • Introduced very wide 512-bit SIMD unitsto the x86 processor design. • Cache coherence multiprocessor system • Up to 4 threads per core • Ultra-wide ring memory bus • Project was terminated on may 2010

Xeon PHI! • The Larrabee project gave birth to the Xeon Phi family of processors: • Knights Ferry (May 2010) • 32 cores, up to 750 GFLOPS • Knights Corner (Nov. 2011) • 60 cores, up to 1.2 TFLOPS • Knights Landing (June 2013) • 72 cores, up to 3 TFLOPS!!!

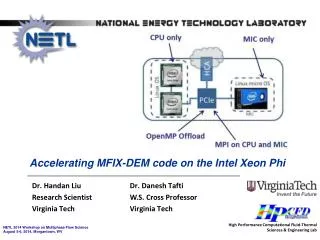

Programing for Xeon PHI (MIC) • Programing for a MIC processor is almost transparent in comparison to normal CPU’s • Standard programing languages: C/C++ and Fortran • Standard parallel programming tools: OpenMP & MPI • MPI can be executed on both host and on the coprocessor • Any code can run on MIC, not just kernels • Optimizing for MIC is similar to optimizing for normal CPUs

Supercomputing • Xeon Phi provide 8 out of 10 PFLOPS of “Stampede” super computer. • Tianhe-2, 2013’s world’s fastest SC, is based on Knights Corner technology

Bibliography • www.wikipedia.com • www.extremetech.com • www.intel.com • www.tacc.utexas.edu • www.upi.com • www.nvidia.com • www1.cse.wustl.edu