Portable Heart Attack Detector (PHAD) Mid Semester Presentation

140 likes | 280 Vues

Supervisor Daniel Alkalay. System architectures Nir Gluzman Alexei Iolin. Technion – Israel Institute of Technology Department of Electrical Engineering High-Speed Digital Systems Lab. Portable Heart Attack Detector (PHAD) Mid Semester Presentation. May 25, 2005. AGENDA.

Portable Heart Attack Detector (PHAD) Mid Semester Presentation

E N D

Presentation Transcript

Supervisor Daniel Alkalay System architectures Nir Gluzman Alexei Iolin Technion – Israel Institute of Technology Department of Electrical Engineering High-Speed Digital Systems Lab Portable HeartAttack Detector(PHAD)Mid Semester Presentation May 25, 2005

AGENDA • Project objective • System block diagram • Project status • Implementation problems • Next steps

PXI-7831R Project objective • Develop a system that measures and displays RR-rate, ST-elevation and alert to wide-QRS. • Implement the system on National-Instrument(*)Real-Time FPGA development environment using LabView graphical language. (*) website: http://ni.com

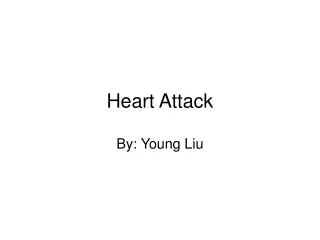

R T P Q S Basic ECG complex

Biosensors A/D interface Detection of ECG characteristic pointswith DWT (Discrete Wavelet Transform) Detection of RR-rate, ST-elevation, wide-QRS Abnormalitiesalert System block diagram

Subject Time period (weeks) Study of NI/FPGA & LabView development environment 3 Implementation 5 Design verification 2 Limited clinical experiments (optional) 1 Final report and project summary 2 Project status

Implementation problems DWT block • ECG characteristic points are detected with DWT (Discrete Wavelet Transform). Source: A wavelet-based ECG delineator: evaluation on standard databases, IEEE Transaction on biomedical engineering, April 2004.

Implementation problems DWT block(cont.) • Two filter-bank implementation for DWT: • Mallat’s algorithm (original design). • “Algorithme à trous” (implementation without decimation).

Implementation problems DWT block(cont.) • Lab experience with NI/FPGA implementation for FIR filters and decimators is limited (because it’s a new system). • Decimators implementation with current version of NI/FPGA modules is complicated. • Decision block adjustment is needed if we re-design DWT block (Mallat algorithme à trous) .

R-trigger block Implementation problems Decision block • Block is based on running RMS calculations for ‘R’ detection.

Implementation problems Decision block(cont.) • Current version of NI/FPGA doesn’t include an RMS module. • Running RMS can be implemented in software (“host”). • Host disadvantage - RMS parallel calculations cannot be implemented.

Implementation problems Floating point VS. fix point • NI/FPGA calculations are done in fix point. • DWT block is based on FIR filters loss of filter stability isn’t expected. • System performance degradation due to the use offix-point is expected to be low.

Next steps • Re-design of DWT block (Mallat algorithme à trous) and decision block. • Consulting with NI Israeli representative regarding improved DSP modules for FPGA: • Meeting is scheduled to 1.6.05. • List of questions were emailed to NI representative abroad. • Due to time constraints we put our effort on system re-designing for NI/FPGA current capabilities.