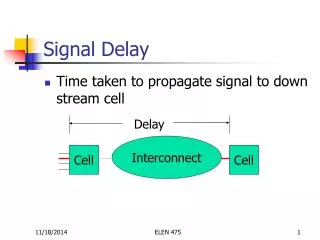

Transport and Inertial Delay Mechanisms in Signal Processing Architectures

E N D

Presentation Transcript

Delay Mechanisms transport | [reject time_exp] inertial • Transport: Ideal transmission line • Inertial: Model rejection of short pulses

Transport Delay entitytransp_dlyis end entitytransp_dly ; ---------------------------------------------------------------- architecture test oftransp_dlyis signal line_in, line_out : bit := '0'; begin transmission_line : process (line_in) is begin line_out <= transport line_in after 500 ps; endprocess transmission_line; ---------------- stimulus : processis begin line_in <= '1' after 2000 ps, '0' after 4000 ps, '1' after 6000 ps, '0' after 6200 ps, '1' after 8000 ps, '0' after 8200 ps, '1' after 8300 ps, '0' after 8400 ps; wait; end process stimulus; end architecture test;

Transport Delay entitytransp_dly1is end entitytransp_dly1 ; architecture test oftransp_dly1is signal a, z : bit; begin asym_delay : process (a) is constant Tpd_01 : time := 800 ps; constant Tpd_10 : time := 500 ps; begin if a = '1' then z <= transport a after Tpd_01; else -- a = '0‘ z <= transport a after Tpd_10; end if; end process asym_delay; stimulus : processis begin a <= '1' after 2000 ps, '0' after 4000 ps, '1' after 6000 ps, '0' after 6200 ps; wait; end process stimulus; end architecture test;

Inertial Delay entityinertial_dlyis end entityinertial_dly; ---------------------------------------------------------------- architecture test ofinertial_dlyis signal top_a, bottom_a : bit := '0'; signal top_y, bottom_y : bit; begin inv_top : process (top_a) is begin top_y <= inertialnot top_a after 3 ns; end process inv; ---------------- stimulus_inertial_dly : process is begin top_a <= '1' after 1 ns, '0' after 6 ns, '1' after 8 ns; wait; end process stimulus_inertial_dly ; end architecture test;

Inertial Delay entityinertial_dly1is end entityinertial_dly1; ---------------------------------------------------------------- architecture test ofinertial_dly1is signal top_a, bottom_a : bit := '0'; signal top_y, bottom_y : bit; begin inv_bottom : process (bottom_a ) is begin bottom_y <= reject 2 ns inertialnot bottom_a after 3 ns; end process inv; ---------------- stimulus_inertial_dly1 : process is begin bottom_a <= '1' after 1 ns, '0' after 6 ns, '1' after 9 ns, '0' after 11.5 ns, '1' after 16 ns, '0' after 18 ns, '1' after 19 ns, '0' after 20 ns; wait; end processstimulus_inertial_dly1 ; end architecture test;

Conditional Signal Assignment • name <= [delay_mechanism] {waveform when bool_expr else} waveform [when bool_expr];

zmux : z <= d0 when sel1 = '0' and sel0 = '0' else d1 when sel1 = '0' and sel0 = '1' else d2 when sel1 = '1' and sel0 = '0' else d3 when sel1 = '1' and sel0 = '1'; zmux : process is begin if sel1 = '0' and sel0 = '0' then z <= d0; elsif sel1 = '0' and sel0 = '1' then z <= d1; elsif sel1 = '1' and sel0 = '0' then z <= d2; elsif sel1 = '1' and sel0 = '1' then z <= d3; end if; wait on d0, d1, d2, d3, sel0, sel1; end process zmux; Conditional Signal Assignment

Selected Signal Assignment • with expr select name <= [delay_mechanism] {waveform when choices,} waveform when choices;

alu : with alu_function select result <= a + b after Tpd when alu_add | alu_add_unsigned, a - b after Tpd when alu_sub | alu_sub_unsigned, a and b after Tpd when alu_and, a or b after Tpd when alu_or, a after Tpd when alu_pass_a; alu : process is begin case alu_function is when alu_add | alu_add_unsigned => result <= a + b after Tpd; when alu_sub | alu_sub_unsigned => result <= a - b after Tpd; when alu_and => result <= a and b after Tpd; when alu_or => result <= a or b after Tpd; when alu_pass_a => result <= a after Tpd; end case; wait on alu_function, a, b; end process alu; Selected Signal Assignment