Registers and Counters

320 likes | 659 Vues

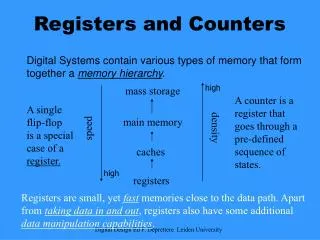

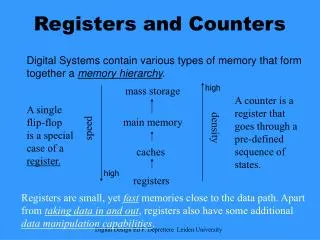

mass storage. main memory. density. speed. caches. registers. Registers and Counters. Digital Systems contain various types of memory that form together a memory hierarchy. high. A counter is a register that goes through a pre-defined sequence of states. A single flip-flop

Registers and Counters

E N D

Presentation Transcript

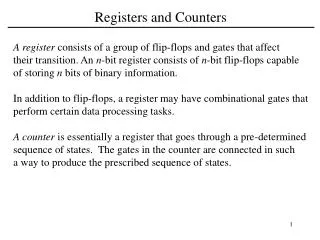

mass storage main memory density speed caches registers Registers and Counters Digital Systems contain various types of memory that form together a memory hierarchy. high A counter is a register that goes through a pre-defined sequence of states. A single flip-flop is a special case of a register. high Registers are small, yet fast memories close to the data path. Apart from taking data in and out, registers also have some additional data manipulation capabilities. Digital Design Ed F. Deprettere Leiden University

REG Clear Clear = 1 all Q = 0 D0 D1 D2 D3 Q0 Q1 Q2 Q3 Clock from 0 to 1 Q(t+1) = D(t) A simple register 4 D-type flip-flops: positive edge triggered with negative logic asynchronous reset or clear input. Reading in data into the register is called loadingthe register. The loading is done in parallel if the four data bits are loaded simultaneously with a common clock. symbol Digital Design Ed F. Deprettere Leiden University

Loading on each clock pulse is (often) undesirable More control needed: Clock Load C inputs Register With Load Control C follows clock if Load is high ? clock skew ? • This is called clock gating. Take care! • What happens when 'Load' changes when the clock is low Clock and Gated Clock are not perfectly synchronized: a flip-flop using Clock And a flip-flop using Gated Clock don’t get activated at the same time. Digital Design Ed F. Deprettere Leiden University

Gating clock leads to clock skew: there is a propagationtime between the main clock and the C-inputs of various flip-flops, which are supposed to sense the same unique clock(t) in a clocked synchronous sequential circuit. Need some other mechanism: D = Load +DataIn Better Register With Load Control • When Load = 0, FF content copied to itself (to get ‘no-change’!) • Build registers from these • General principle: don't gate the clock! Four times this structure to build 4-bit register with parallel load Digital Design Ed F. Deprettere Leiden University

Move bits laterally , west-to-east, east-to-west, north-to-south, south-to-north, or a combination of these, unidirectional or bi-directional. Principle: chain flip-flops: Serial Input Serial output SI D D D D SO C C C C Clock Clock SRG 4 SI SO The Shift Register Circuit Symbol Digital Design Ed F. Deprettere Leiden University

S A Cout B FA FA FA FA Cin S3 S2 S1 S0 example: the serial adder Recall: Parallel Adder is not really parallel! Carry ripples through roughly 2n gates: long propagation time. We can do better! Or, we can reuse a single FA: Serial Adder Idea: Use shift registers to store intermediate results. How? Digital Design Ed F. Deprettere Leiden University

Register A C SRG 4 FA Reset Clear X SI SO S Y C Shift Z Register B Clock SRG 4 C Clear Reset D SI SO Serial In C R Reset Ignoring Registers: Parallel adder is CC Serial adder is SC Serial addition is also called Software Addition. What about Power Dissipation? We say that the parallel adder has its states in space, the serial adder has its states in time. A typical example of space-time trade-off. More hardware faster. Less hardware slower. Digital Design Ed F. Deprettere Leiden University

Serial Input From Bus Serial output SI D D D D SO C C C C Clock Function Table SHR 4 Shift Load 0 0 no change 0 1 parallel load 1 X shift down Shift Load Serial ! SI D0 D1 D2 D3 Q0 Q1 Q2 Q3 To Bus Serie-Parallel and Parallel-Serie Serial In, Parallel Out. Parallel In, Serial Out. Digital Design Ed F. Deprettere Leiden University

SHR 4 S1 S2 LSI D0 D1 D2 D3 RSI Q0 Q1 Q2 Q3 D Qi-1 Control Flip-flop Register Mode Operation C L(R)SI Left(Right) Serial In S1 S0 D S MUX 0 0 0 Qi No Change 0 1 Qi-1 Shift Down 1 0 Qi+1 Shift Up 1 1 D1 Par. Load S 1 D Qi C 0 1 Di 2 3 D Qi+1 C Clock Bi-directional Shift Register Here is an up-down (bi-directional) shift register. Function Table If Qi = Q0, then Qi-1 = SI Digital Design Ed F. Deprettere Leiden University

Very useful device Produce time delay Example: 1 second-clock, count to 60 1 minute delay Control computation Example: serial adder, add 16 bits count to 16 Types of counters Asynchronous (ripple counter) — simple, but troublesome Synchronous counters (best kind) Up, down, special counters Counters with different periods Counters Digital Design Ed F. Deprettere Leiden University

Upward Counter Downward counter Gray code counter Q3 Q2 Q1 Q0 Q3 Q2 Q1 Q0 Q3 Q2 Q1 Q0 0 0 0 1 1 1 1 0 0 0 0 0 0 0 0 1 1 1 1 0 0 0 0 1 0 0 1 0 1 1 0 1 0 0 1 1 0 0 1 1 1 1 0 0 0 0 1 0 0 1 0 0 1 0 1 1 0 1 1 0 0 1 0 1 1 0 1 0 0 1 1 1 0 1 1 0 1 0 0 1 0 1 0 1 0 1 1 1 1 0 0 0 0 1 0 0 1 0 0 0 0 1 1 1 1 1 0 0 1 0 0 1 0 1 1 0 1 1 0 1 1 0 1 0 0 1 0 1 1 1 1 1 1 0 1 1 0 1 0 0 1 1 1 0 1 1 0 0 0 0 1 1 1 0 1 0 1 1 0 1 0 0 1 0 1 0 1 1 1 1 1 0 0 0 0 1 1 0 0 1 1 1 1 1 0 0 0 0 1 0 0 0 Counting Sequences Counters go through prescribed sequence of states upon application of input pulses (clock or other signals). Binary counter Binary counter Digital Design Ed F. Deprettere Leiden University

Clock Logic 1 T T T T C C C C • • R R • R R Q Q Q Q 1 3 2 0 Ripple Counter with T Flip-Flops Recall: T flip-flop is JK flip-flop with J=K. Have seen this before. Remember? Features: Simple Clock input from logic circuits — not quite clock synchronous Digital Design Ed F. Deprettere Leiden University

Q1 Q(t) Q(t+1) J K J K Q(t+1) 1 • 0 0 0 x • 0 1 1 x • 0 x 1 • 1 1 x 0 0 0 Q(t) 0 1 0 1 0 1 1 1 Q(t) Q2 x x x x Q3 x x x x Q0 Present State Next State Input Equations Q3 Q2 Q1 Q0 Q3 Q2 Q1 Q0 J3 K3 J2 K2 J1 K1 J0 K0 0 0 0 0 0 0 0 1 0 x 0 x 0 x 1 x ------------ 0 1 1 1 1 0 0 0 1 x x 1 x 1 x 1 ------------ 1 1 1 1 0 0 0 0 x 1 x 1 x 1 x 1 How to design counters? Recall: JK flip-flop Characteristic table excitation equations J3 = K3 = Q0Q1Q2 State Table and Input Equations Digital Design Ed F. Deprettere Leiden University

Notice: Jk = Kk Toggle Flip-flop Qk-1 (k-1)K CTR 4 Qk kJ EN Q0 Q1 Q2 Q3 CO Ck kK Q3 Carry out J3 = K3 = Q0Q1Q2 ENJ2 = K2 = Q0Q1 EN J1 = K1 = Q0 EN J0 = K0 = EN Symbol Jk = Kk = Q0Q1…Qk-1EN If k = 0, then (-1)K = EN, Q-1 = 1. Design with D flip-flops: similar. Result: Qk(t+1) = Dk = Qk (Q0Q1…Qk-1EN) Digital Design Ed F. Deprettere Leiden University

CTR 4 CTR 4 Load Count D0 D1 D2 D3 Load Count D0 D1 D2 D3 Q0 Q1 Q2 Q3 C0 1 Q0 Q1 Q2 Q3 C0 0 Many more counters can be thought of. Up-down counters: can go both ways for k = 0 step +1 to 7, or for k = 7 step –1 to 0 increment decrement Counters with parallel load: can be initialized N = 1; for k = N step +1 to N+7 parametrized Symbol Example: BCD counter. Digital Design Ed F. Deprettere Leiden University

n data input lines k address lines RAM 2k words Read Write n bits per word n data output lines Random Access Memories Recall: registers are small, yet fast place holders with elementary operations. When going one step up in the memory hierarchy, we find: Example: Read-only memory (ROM) Random Access Memory (RAM) k = 10 is 1K words N = 16 = 2 bytes: 2K byte RAM Time to get in (write) a word and time to get out (read) a word is independent of the location (address) of the word in memory. Word is a number of bytes. Digital Design Ed F. Deprettere Leiden University

memory content first byte second byte memoryaddress binarydecimal 0000000000 0 0000000001 1 0000000010 2 1111111101 1021 1111111110 1022 1111111111 1023 The operations: Write: store data from … into RAM - apply binary address of location to address lines -apply data bits of word to bestored to data input lines - active R/W signal (R/W = 0) Read: load data from RAM into … - apply binary address of word to read to address lines - activate R/W signal(R/W = 1) Current RAMs are real big. For Multimedia applications, they are way too small. Digital Design Ed F. Deprettere Leiden University

Types of RAMs Static Ram (SRAM) : latches are basic storage units. Dynamic Ram (DRAM) : capacitors (charge reservoirs) are the basic storage units. SRAM: larger, higher power consumption, faster DRAM: smaller, lower power consumption, slower DRAM needs refreshing because capacitors leak. Both types are volatile : power off is loss of data. Write to disc before power switch-off (disc is non-volatile) Digital Design Ed F. Deprettere Leiden University

Select B C S R C • B Select = 0 : (S = R =0) : hold Q; C = C = 0. Select = 1: S = B, C = Q Building SRAMs A RAM of m words of n bits consists of an array of n m binary storage cells plus circuitry. A RAM cell is typically designed as an electronic circuit not a logic circuit. (a matter of efficiency). But it can be modeled as a logic circuit (not so for DRAM). Digital Design Ed F. Deprettere Leiden University

Address lines A3 3 2 1 0 4-to-16 DECODER 2 2 2 2 word select A2 0 1 2 3 14 15 RAM cell 4 A1 16 * 1 RAM Dout A0 D in R/W RAM cell EN Dout Data Out Din Data In R/W Read/Write RAM select Bit Select The RAM bit slice RAMs are built recursively. The RAM bit slice is a one-bit-word RAM The buffer is a three state-buffer. Digital Design Ed F. Deprettere Leiden University

IN IN OUT OUT EN EN OL S one in per C line connecting all B one in per C x line connecing all B x x x x Data in S Q R • Read/Write Bit select The three-state buffer is an electronic device. OUT = IN if EN = 1. OUT undefined if EN = 0. The EN = 0 state is called Hi-Z (high impedance). Several three-state buffers can be connected to the same output line (OL) provided only one EN is 1 at any point in time. Behaves like multiplexer. The write logic. The read logic. x Array logic 4-input OR: 3 connected. Data out Bit select Digital Design Ed F. Deprettere Leiden University

0 1 2 3 A3 1 0 2 2 A2 2-to-4 decoder Data in data out R/W Bit S Data in data out R/W Bit S Data in data out R/W Bit S Data in data out R/W Bit S Data input Read/Write Data out 0 1 2 3 2-to-4 decoder 1 0 2 2 enable Row 2 Colomn 1 A1 A0 Building larger RAMs Instead of using word select use row selelct and colom select. 16 1 RAM as a 4 4 array instead of a 16 1 array. Address 1001 (cell 9) Digital Design Ed F. Deprettere Leiden University

Qi-1 (SI if i =0) Shift Load D Qi Di C i = 0, 1, 2, 3 Digital Design Ed F. Deprettere Leiden University

from Q0 to XOR from Q0 EN EN to XOR from Q1 from Q2 from Q3 CO CO The chain of AND gates in the JK based and D based binary counters form a large ripple path (serial gating: slow operation). Parallel gating (parallel counters) goes much faster : Digital Design Ed F. Deprettere Leiden University

80ns 20nsec T1 T2 T3 T4 T1 Clock 5ns Address address valid Enable address lines stable R/W Data In data valid 75ns Memory R & W Cycles Memory access should be as fast as possible. Therefore the timing must be well defined. Storing one word is called a write cycle: Write cycle time Digital Design Ed F. Deprettere Leiden University

80ns 20nsec T1 T2 T3 T4 T1 Clock 5ns Address address valid address line stable Enable address lines stable R/W Data Out data stable 65ns Loading one word is called a read cycle. Notice: reading is non-destructive Read cycle is slightly different from write cycle. Access time Digital Design Ed F. Deprettere Leiden University