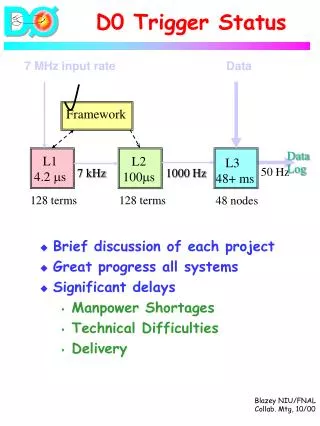

Progress Update on DØ Trigger Upgrade Technical Work Breakdown Structure (WBS) 1.2

This document outlines the current advancements and activities related to the DØ Trigger Upgrade, specifically WBS 1.2, focusing on Level 1 projects such as Calorimeter, Cal-track matching, and Tracking modifications. Key developments include the completion of ADF prototype schematics and the progress of the Analog Splitter designed for in-situ testing. It covers integration strategies for the ADF and TAB prototypes, upcoming simulation studies, and the continued efforts towards firmware development. Workshops and meetings with engineers and physicists have been pivotal in decision-making processes.

Progress Update on DØ Trigger Upgrade Technical Work Breakdown Structure (WBS) 1.2

E N D

Presentation Transcript

DØ RunIIb Trigger UpgradeTechnical Progress WBS 1.2 Darien Wood, Northeastern Univ. for the DØ Trigger Upgrade Group

WBS 1.2: Trigger Upgrade H. Evans (Columbia), D. Wood (Northeastern) WBS 1.2.1: Level 1 Calorimeter M.Abolins(MSU), H.Evans(Columbia), P.LeDu (Saclay) WBS 1.2.2: Level 1 Cal-track match K. Johns (Arizona) WBS 1.2.3: Level 1 Tracking M. Narain (Boston) WBS 1.2.4: Level 2 Beta upgrade R. Hirosky (Virginia) WBS 1.2.5: Level 2 STT upgrade U. Heintz (Boston) WBS 1.2.6: Trigger Simulation M. Hildreth (ND), E. Perez (Saclay) Outline Level 1 projects underway • Level 1 Calorimeter • Level 1 Cal-track matching • Level 1 Tracking • Trigger simulations Level 2 projects (not discussed here) • L2 Beta upgrade & STT upgrade • Later start in schedule • VTM’s procured for STT (part of larger order)

Saclay ADC+Digitial Filter (ADF) ADF timing distribution board Analog splitter (for in-situ tests) ADF Crate/backplane Nevis Trigger algorithm board (TAB) Global Algorithm Board (GAB) Crates for TAB/GAB Test system for ADF-to-GAB cables WBS 1.2.1: Calorimeter Trigger Upgrade

ADF: Saclay • ADF prototype schematics • All components chosen • Should be verified in a few weeks: end of prototype design • ADF prototype PCB design • Layout should start in about 1 week • Expect 3-4 weeks for layout

Analog Splitter: Saclay & MSU • Analog splitter: allows in-situ test of digital filtering with real signals • Designed and tested at Saclay • Shipped to MSU Dec 20th: tested there • Installed in DØ L1Cal trigger (run IIa) during current shutdown • Noise tests in progress • Tests with beam (w/ splitter vs. w/o splitter) to follow

TAB prototype: Nevis • Design essentially finished (mod’s driven by layout) • Layout/Schematics well advanced • Recent design issues • Use thresholds to deal with digital filter signal truncation • ADF-to-TAB cable mapping scheme adopted • Density of cables → no room for standard VME backplane • Slow communication w/ TABs & GAB designed • Full access to TAB/GAB using VME-transparent interface • Timing/control signal distribution

Transatlantic communication & plans • Trigger Workshop held Nov 4-6 at Saclay • Participants: Engineers & physicists from Saclay, Columbia, MSU, Brown, NeU • Many decisions made about ADF-TAB data transfer, system commissioning • Integration plans • ADF + TAB prototype integration tests scheduled at Fermilab this summer • More detailed plan for commissioning of final system is being developed

Cal-Trk match: Arizona • Uses “L1mu” electronics, apart from specialized “flavor board” • Flavor board (MTFB) prototype design >90% complete • Some procurements anticipated for next month MTFB (scint flavor)

L1 CTT: Boston Univ. • Firmware design for target algorithm began in Nov • “front end” and “back end” code from Run IIa rewritten – latency reduced • Ongoing work on maps of single fibers

Simulation • Studies of effects of trigger tower thresholds on L1cal global sums (missing ET) • L1Cal tau algorithm included in trig sim • Output of Run IIb L1 cal interfaced to standard DØ framework simulation package • Simulation of Cal-track matching progressing • CTT as-built geometry and beam offsets incorporated into simulation • Beam offsets up to ~1mm to not affect efficiency of Run IIb equations

Summary • L1cal • ADF and TAB prototypes near the end of design phase – layouts soon • Analog splitter installed at DØ • Integration tests planned for Summer • L1 cal-track • Design of prototype flavor board nearly complete • L1 CTT • Progress in firmware – on schedule • Simulation • Continued support of design efforts and development of standard simulation packages