Clock domains & divider Clock & reset distribution

300 likes | 471 Vues

Clock domains & divider Clock & reset distribution. A. Kluge Feb 5 & 6, 2013. clk domains. pixel_hit clk_config clk_dll clk_sync ( hronous ) clk_serial clk_multi_serial. clk_config. clk_multi_serial. clk_sync. clk_serial. clk_dll. Clk distribution: serial 3.2 Gbit /s.

Clock domains & divider Clock & reset distribution

E N D

Presentation Transcript

Clock domains & dividerClock & reset distribution A. Kluge Feb 5 & 6, 2013

clk domains • pixel_hit • clk_config • clk_dll • clk_sync(hronous) • clk_serial • clk_multi_serial A. Kluge

clk_config clk_multi_serial clk_sync clk_serial clk_dll A. Kluge

Clk distribution: serial 3.2 Gbit/s A. Kluge

Clk distribution: serial 3.2 Gbit/s 30 bit shift register every 6th clock cycle one word is sent to serializer every 53 MHz new word of 48 bits on 4 outputs 48/4 ports * 53 MHz = 640 MHz A. Kluge

clk domain crossing • pixel_hit clk_synchitArbiter • clk_sync clk_serial • clk_sync clk_multi_serial • clk_config clk_sync • clk_dll clk_synctdc, qchip A. Kluge

clk_config clk_multi_serial clk_sync clk_serial clk_dll A. Kluge

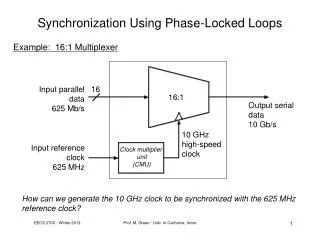

clk_sync clk_serial • clock_enable_generator • frequ_clk_sync = 6 * frequ_clk_fifo_read = 6 * frequ_enable_clk_sync • 12 * for modes 1, 4, 6 • qchip runs on clk_sync • flip flops are enabled only upon enable_clk_sync • TDC is read-out only every 6th (12th) clk_sync cycle • serializer is loaded only every 6th(12th) clk_sync cycle A. Kluge

clock_enable_generator • Serializerprovides sync signal - clk_fifo_read • frequency = parallel_word_freqency • falling edge + 3 (3.5) serial_frequ/2 marks parallel load time • clk_enable_generator • synchronizes clk_fifo_read to clk_sync domain • waits for time-out • measures position of clk_fifo_read, once • does not re-adjust later-on • produces enable_clk_sync pulse around rising edge of clk_fifo_read • marks safe parallel_word change time A. Kluge

clk_sync clk_serial first_enable_after_delay A. Kluge

clock_enable_generator • hold/setup [ns] • mode 0: 11.6-9.5 / 13.4/15.5 • mode 1: 15.7-13.6 / 9.3 – 11.4 • mode 2: 10.3 – 7.2 / 8.5 – 11.6 A. Kluge

clk_enable_generator A. Kluge

clk_config clk_multi_serial clk_sync clk_serial clk_dll A. Kluge

multi_serial_synchronisationclk_sync clk_multi_serial • synchronizes enable_clk_syncinto clk_multi_serial domain • measures the position of enable_clk_sync once • locks parallel_load time in middle of two enable_clk_sync pulses • hold/setup time of ~ 9 ns A. Kluge

multi_serial_synchronisationclk_sync clk_multi_serial A. Kluge

multi_serial_synchronisationclk_sync clk_multi_serial A. Kluge

clk_config clk_multi_serial clk_sync clk_serial clk_dll A. Kluge

clk_config clk_sync CLK_SYNC CLK_SYNC CLK_SYNC CLK_SYNC A. Kluge

Operation modes A. Kluge

PLL & clock divider A. Kluge

clock distribution • Clock_sync on 5 outputs @PLL&Serializerblock • 4 x quarter chip + 5 x TDC & 1 x configuration block • distributed on the top levelwith clock tree • TDC distributes clock to dll_state_machine_and_lock_detector internally A. Kluge

Reset distribution • Reset signal arrives from from two sources • externally from a low active input pad • internally from the configuration block • reset_synchronizer_asynchron • synchronizes the asynchronously arriving external reset_global_isignal to clk_syncin the config block and in the 4 quarter chips blocks A. Kluge

reset_synchronizer_asynchron A. Kluge

Reset distribution • quarter chip distributes reset signal to TDC blocks • In TDC reset is synchronized using reset_synchronizerblock. • Internally TDC forwards reset to dll_state_machine_and_lock_detector block • where again a reset_synchronizeris used. • Staged reset distribution allows simpler propagation delay management • Drawback that all TDCpix blocks are reset in stages of 3 clock cycles • no impact on functionality • All synchronizers triplicated and internal reset signals are forwarded as high active signals whereas external reset_global_iinput is low active A. Kluge

Reset coarse counter • External signal which sets the coarse counter to 0 • Connected to dll_clk_fanout • fowardsit to TDC as a one clock cycle long pulse • to the quarter chip as a two cycle long pulse • Two cycle long pulse is needed as the copy of the coarse counter in the qchip is running on clk_sync on not on clk_dll as in the TDC • If clk_sync is slower than clk_dll one clk_dll long pulses might not be registered by the qChip • Synchronisationof reset_coarse_count uses reset_synchronizer_asynchron • Reset_coarse_counteralso can be initiated by software via the configuration block A. Kluge

Clock and reset distribution A. Kluge