A presentation on Counters (second)

A presentation on Counters (second). Information obtained using educative resources from the WWW. http://www.eelab.usyd.edu.au/digital_tutorial/part2/counter02.html http://en.wikipedia.org/wiki/Counter. Review Counters : Two principal categories.

A presentation on Counters (second)

E N D

Presentation Transcript

A presentation on Counters(second) Information obtained using educative resources from the WWW. http://www.eelab.usyd.edu.au/digital_tutorial/part2/counter02.html http://en.wikipedia.org/wiki/Counter

ReviewCounters: Two principal categories • Counters are divided in two categories, these are: • Asynchronous (Ripple) Counters - the first flip-flop is clocked by the external clock pulse, and then each successive flip-flop is clocked by the Q or Q' output of the previous flip-flop. • Synchronous Counters - all memory elements are simultaneously triggered by the same clock.

Two-bit asynchronous counter • A two-bit asynchronous counter is shown on the left. • It uses two J-K flip flops.

Synchronous counters • In synchronous counters, the clock inputs of all the flip-flops are connected together and are triggered by the input pulses. • Thus, all the flip-flops change state simultaneously (in parallel). • The circuit below is a 3-bit synchronous counter.

Synchronous counters • The J and K inputs of FF0 are connected to HIGH. • FF1 has its J and K inputs connected to the output of FF0, and the J and K inputs of FF2 are connected to the output of an AND gate that is fed by the outputs of FF0 and FF1.

Synchronous counter • Pay attention to what happens after the 3rd clock pulse. • Both outputs of FF0 and FF1 are HIGH. • The positive edge of the 4th clock pulse will cause FF2 to change its state due to the AND gate. Q0: FF0 Q1: FF1 Q2: FF2

Synchronous counter • The count sequence for the 3-bit counter is shown on the right.

Synchronous counter • The most important advantage of synchronous counters is that there is no cumulative time delay because all flip-flops are triggered in parallel. • Thus, the maximum operating frequency for this counter will be significantly higher than for the corresponding ripple counter.

SynchronousDecade Counters • Similar to an asynchronous decade counter, a synchronous decade counter counts from 0 to 9 and then recycles to 0 again. • This is done by forcing the 1010 state back to the 0000 state. • This so called truncated sequence can be constructed by the following circuit.

SynchronousDecade Counters • From the sequence on the left, we notice that: Q0 toggles on each clock pulse.

SynchronousDecade Counters • Q1 changes on the next clock pulse each time Q0=1 and Q3=0.

SynchronousDecade Counters • Q2 changes on the next clock pulse each time Q0=Q1=1. • Q3 changes on the next clock pulse each time Q0=1, Q1=1 and Q2=1 (count 7), or when Q0=1 and Q3=1 (count 9).

SynchronousUp-Down Counters • A circuit of a 3-bit synchronous up-down counter and a table of its sequence are shown below. • Similar to an asynchronous up-down counter, a synchronous up-down counter also has an up-down control input. • It is used to control the direction of the counter through a certain sequence.

SynchronousUp-Down Counters • An examination of the sequence table shows: for both the UP and DOWN sequences, Q0 toggles on each clock pulse.

SynchronousUp-Down Counters • for the UP sequence, Q1 changes state on the next clock pulse when Q0=1.

SynchronousUp-Down Counters • for the DOWN sequence, Q1 changes state on the next clock pulse when Q0=0.

SynchronousUp-Down Counters • for the UP sequence, Q2 changes state on the next clock pulse when Q0=Q1=1. • for the DOWN sequence, Q2 changes state on the next clock pulse when Q0=Q1=0.

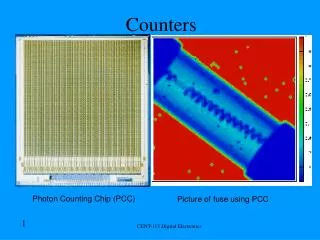

Applications • Digital counters are very useful in many applications. • They can be easily found in digital clocks and parallel-to-serial data conversion (multiplexing).

Applications • A group of bits appearing simultaneously on parallel lines is called parallel data. • A group of bits appearing on a single line in a time sequence is called serial data. • Parallel-to-serial conversion is normally accomplished by the use of a counter to provide a binary sequence for the data-select inputs of a multiplexer, as illustrated in the circuit below.

Applications • The Q outputs of the modulus-8 counter are connected to the data-select inputs of an eight-bit multiplexer. • The first byte (eight-bit group) of parallel data is applied to the multiplexer inputs. • As the counter goes through a binary sequence from 0 to 7, each bit beginning with D0, is sequentially selected and passed through the multiplexer to the output line.

Applications • After eight clock pulses, the data byte has been converted to a serial format and sent out on the transmission line. • Then, the counter recycles back to 0 and converts another parallel byte sequentially again by the same process.

Merry Christmas, Happy New Year and Happy 3 Kings Day! STUDY!!!