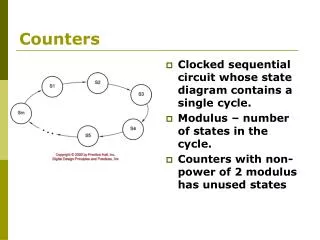

Counters

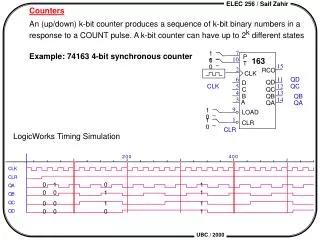

Counters. Mano & Kime Sections 5-4, 5-5. Counters. Ripple Counter Synchronous Binary Counters Design with D Flip-Flops Design with J-K Flip-Flops Counters in VHDL. Counters ---. A 4-bit Ripple Counter. Less Significant Bit output is Clock for Next Significant Bit!

Counters

E N D

Presentation Transcript

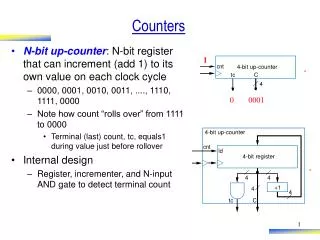

Counters Mano & Kime Sections 5-4, 5-5

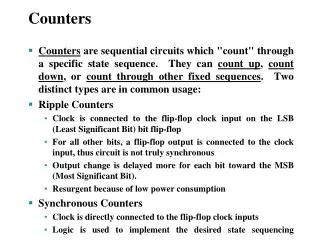

Counters • Ripple Counter • Synchronous Binary Counters • Design with D Flip-Flops • Design with J-K Flip-Flops • Counters in VHDL

A 4-bit Ripple Counter Less Significant Bit output is Clock for Next Significant Bit! (Clock - active low) Recall...

J-K Flip-Flop from a D Flip-Flop DQ = J & !Q # !K & Q DQ = Q DQ = 0 DQ =!Q # Q = 1 DQ = !Q

Counters • Ripple Counter • Synchronous Binary Counters • Design with D Flip-Flops • Design with J-K Flip-Flops • Counters in VHDL

State Q2 Q1 Q0 Q2.D Q1.D Q0.D D Q Q0.D Q0 CLK !Q s0 0 0 0 0 0 1 s1 0 0 1 0 1 0 s2 0 1 0 0 1 1 s3 0 1 1 1 0 0 s4 1 0 0 1 0 1 s5 1 0 1 1 1 0 s6 1 1 0 1 1 1 s7 1 1 1 0 0 0 D Q Q1.D Q1 CLK !Q D Q Q2.D Q2 CLK !Q Divide-by-8 Counter

State Q2 Q1 Q0 Q2.D Q1.D Q0.D s0 0 0 0 0 0 1 s1 0 0 1 0 1 0 s2 0 1 0 0 1 1 s3 0 1 1 1 0 0 s4 1 0 0 1 0 1 s5 1 0 1 1 1 0 s6 1 1 0 1 1 1 s7 1 1 1 0 0 0 Divide-by-8 Counter Q1 Q0 00 01 11 10 Q2 1 0 1 1 1 1 Q2.D Q2.D = !Q2 & Q1 & Q0 # Q2 & !Q1 # Q2 & !Q0

State Q2 Q1 Q0 Q2.D Q1.D Q0.D s0 0 0 0 0 0 1 s1 0 0 1 0 1 0 s2 0 1 0 0 1 1 s3 0 1 1 1 0 0 s4 1 0 0 1 0 1 s5 1 0 1 1 1 0 s6 1 1 0 1 1 1 s7 1 1 1 0 0 0 Divide-by-8 Counter Q1 Q0 00 01 11 10 Q2 1 1 0 1 1 1 Q1.D Q1.D = !Q1 & Q0 # Q1 & !Q0

State Q2 Q1 Q0 Q2.D Q1.D Q0.D s0 0 0 0 0 0 1 s1 0 0 1 0 1 0 s2 0 1 0 0 1 1 s3 0 1 1 1 0 0 s4 1 0 0 1 0 1 s5 1 0 1 1 1 0 s6 1 1 0 1 1 1 s7 1 1 1 0 0 0 Divide-by-8 Counter Q1 Q0 00 01 11 10 Q2 1 1 0 1 1 1 Q0.D Q0.D = ! Q0

CUPL Simulation Output File

State Q2 Q1 Q0 Q2.D Q1.D Q0.D D Q Q0.D Q0 CLK !Q s0 0 0 0 1 1 1 s1 0 0 1 0 0 0 s2 0 1 0 0 0 1 s3 0 1 1 0 1 0 s4 1 0 0 0 1 1 s5 1 0 1 1 0 0 s6 1 1 0 1 0 1 s7 1 1 1 1 1 0 D Q Q1.D Q1 CLK !Q D Q Q2.D Q2 CLK !Q 3-Bit Down Counter

State Q2 Q1 Q0 Q2.D Q1.D Q0.D s0 0 0 0 1 1 1 s1 0 0 1 0 0 0 s2 0 1 0 0 0 1 s3 0 1 1 0 1 0 s4 1 0 0 0 1 1 s5 1 0 1 1 0 0 s6 1 1 0 1 0 1 s7 1 1 1 1 1 0 3-Bit Down Counter Q1 Q0 00 01 11 10 Q2 1 0 1 1 1 1 Q2.D Q2.D = !Q2 & !Q1 & !Q0 # Q2 & Q1 # Q2 & Q0

State Q2 Q1 Q0 Q2.D Q1.D Q0.D s0 0 0 0 1 1 1 s1 0 0 1 0 0 0 s2 0 1 0 0 0 1 s3 0 1 1 0 1 0 s4 1 0 0 0 1 1 s5 1 0 1 1 0 0 s6 1 1 0 1 0 1 s7 1 1 1 1 1 0 3-Bit Down Counter Q1 Q0 00 01 11 10 Q2 1 1 0 1 1 1 Q1.D Q1.D = !Q1 & !Q0 # Q1 & Q0

State Q2 Q1 Q0 Q2.D Q1.D Q0.D s0 0 0 0 1 1 1 s1 0 0 1 0 0 0 s2 0 1 0 0 0 1 s3 0 1 1 0 1 0 s4 1 0 0 0 1 1 s5 1 0 1 1 0 0 s6 1 1 0 1 0 1 s7 1 1 1 1 1 0 3-Bit Down Counter Q1 Q0 00 01 11 10 Q2 1 1 0 1 1 1 Q0.D Q0.D = ! Q0

Up-Down Counter Up-Down Counter clock Q0 Q1 Q2 UD UD = 0: count up UD = 1: count down

Up-Down Counter UD Q2 Q1 Q0 Q2.D Q1.D Q0.D UD Q2 Q1 Q0 Q2.D Q1.D Q0.D 0 0 0 0 0 0 1 0 0 0 1 0 1 0 0 0 1 0 0 1 1 0 0 1 1 1 0 0 0 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 0 1 1 1 0 1 1 1 0 0 0 1 0 0 0 1 1 1 1 0 0 1 0 0 0 1 0 1 0 0 0 1 1 0 1 1 0 1 0 1 1 0 0 0 1 1 1 1 0 1 1 0 0 1 1 1 0 1 0 1 1 1 1 1 1 1 0 Up-Counter Down-Counter

Up-Down Counter Q1 Q0 00 01 11 10 UD Q2 00 01 11 10 Make Karnaugh maps for Q2.D, Q1.D, and Q0.D

Counters • Ripple Counter • Synchronous Binary Counters • Design with D Flip-Flops • Design with J-K Flip-Flops • Counters in VHDL

Synchronous Binary Counters J-K Flip Flop Design of a Binary Up Counter

Synchronous Binary Counters J-K Flip Flop Design of a Binary Up Counter

Synchronous Binary Counters J-K Flip Flop Design of a Binary Up Counter

Synchronous Binary Counters J-K Flip Flop Design of a Binary Up Counter

4 - Bit Counter Logic Diagram

Counters • Ripple Counter • Synchronous Binary Counters • Design with D Flip-Flops • Design with J-K Flip-Flops • Counters in VHDL