Counters

Counters. Switching and Logic Lab Standard Laboratory Exercises. Suggestions and Warnings. Read for detail and comprehension Should be able to complete within normal laboratory period. Make sure you program unused pins as tri-state inputs or you may burnout EPM7128S device on PLDT-2.

Counters

E N D

Presentation Transcript

Counters Switching and Logic Lab Standard Laboratory Exercises

Suggestions and Warnings • Read for detail and comprehension • Should be able to complete within normal laboratory period. • Make sure you program unused pins as tri-state inputs or you may burnout EPM7128S device on PLDT-2.

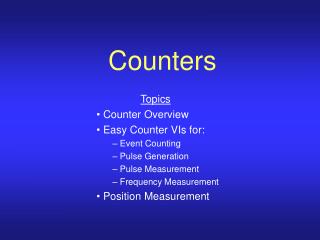

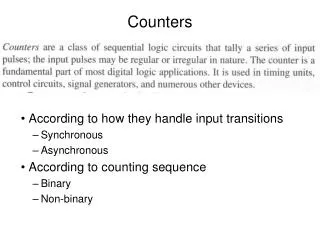

Counters • Project 1 • Decade Counter as Behavioral VHDL • Common Clock with clock enable • Mixed Signal oscilloscope • Project 2 • One-Hundred Second Timer (00 to 99) • Hierarchical Design • Dec7Seg.vhd, Decade.vhd, LPM_Counter.vhd • Timer.bdf

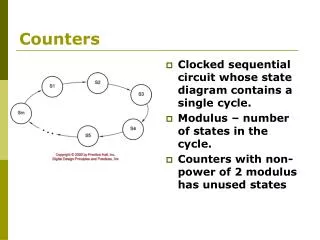

Project 1 – Decade Counter 1001, 0 1000, 0 0111, 0 ClkClkEn’ 0000, 1 0110, 0 ClkClkEn 0100, 0 0011, 0 0101, 0 Others, 0 0010, 0 0001, 0 BCD, Cout State

Updated by port and read by port Decade Entry Statement ENTITY decade IS PORT ( ClkEn,clock : IN BIT; BCD : BUFFER BIT_VECTOR ( 3 downto 0); Cout : OUT BIT); END decade;

Port Mode • Port declaration format: port_name: mode data_type; The mode of a port defines the directions of the signals on that port, and is one of: in, out, buffer, or inout. • An in port can be read but not updated within the module, carrying information into the module. (An in port cannot appear on the left hand side of a signal assignment.) • An out port can be updated but not read within the module, carrying information out of the module. (An out port cannot appear on the right hand side of a signal assignment.)

Port Mode • A buffer port likewise carries information out of a module, but can be both updated and read within the module. • An inout port is bidirectional and can be both read and updated, with multiple update sources possible. • NOTE: A buffer is strictly an output port, i.e. can only be driven from within the module, while inout is truly bidirectional with drivers both within and external to the module.

BCD on both left and right side of assignment operator Transition on signal which is either 1 0 or 0 1 Decade Architecture Statement ARCHITECTURE behavioral OF decade IS BEGIN Decade_Counter: PROCESS BEGIN WAIT UNTIL clock = '1' and clock'event; IF ClkEn='1' THEN CASE BCD IS •••••; END CASE; ELSE BCD <= BCD; Cout <= '0'; END IF; END PROCESS Decade_Counter; END behavioral;

Both sides of signal assignment operator Decade Architecture Statement CASE BCD IS WHEN "0000" => BCD <= “1001"; Cout <= ‘1'; WHEN “1001" => BCD <= “1000"; Cout <= '0'; WHEN “1000" => BCD <= "0111"; Cout <= '0'; WHEN "0111" => BCD <= "0110"; Cout <= '0'; WHEN "0110" => BCD <= "0101"; Cout <= '0'; WHEN "0101" => BCD <= "0100"; Cout <= '0'; WHEN "0100" => BCD <= "0011"; Cout <= '0'; WHEN "0011" => BCD <= “0010"; Cout <= '0'; WHEN “0010" => BCD <= “0001"; Cout <= '0'; WHEN “0001" => BCD <= "0000"; Cout <= ‘0'; WHEN OTHERS => BCD <= "0000"; Cout <= '0'; END CASE;

Full Compile • Analysis and Synthesis (0 errors 0 warnings) • Fitter (0 errors 0 warnings) • Assembler (0 errors 0 warnings) • Timing Analysis (0 errors 1 warnings) • Not Permitted Warning • Define Clock Warning: Found pins functioning as undefined clocks and/or memory enables Info: Assuming node "clock" is an undefined clock

Simulation or Timer.vwf Clock 10 Clock 10 fOSC = 4 MHz thus TOSC = 250 ns 16 x 250 ns = 4000 ns

Mixed Signal Oscilloscope 54645D Via BenchLink Scope Setup File ••••• ••• •• • Provides • Labels • Trigger configuration • Display configuration

Restore Setup on 54622D • Place DOS formatted floppy in desktop drive • Copy setup from web page to floppy • Remove floppy from desktop drive • Place floppy in MSO • Press Save/Restore • Select “Recall” softkey • Scroll to Decade • Press the “Press to Recall” softkey

MSO Image Capture for 54645D • Image | New… • File | Save As… • TIFF • PCX

MSO Image Capture for 54622D • Place DOS formatted floppy in MSO drive • Press Quick Print • Remove floppy from MSO drive • Place floppy in desktop system • Move file from A: to LAB_DAY, Web Drive, or USB Mass Memory Device folder

Similar to Timing Simulation • Labels on D4 to D0 • Scan rate of 500 ns/division • CMOS Threshold • D4 to D0 on all others off • Trigger on rising edge of D4 (slowest repetition rate waveform)

Project Two Dec7Seg Decade LPM_COUNTER Common Clock

Full Compile • Analysis and Synthesis (0 errors 0 warnings) • Fitter (0 errors 0 warnings) • Assembler (0 errors 0 warnings) • Timing Analysis (0 errors 1 warnings) • Not Permitted Warning • Define Clock Warning: Found pins functioning as undefined clocks and/or memory enables Info: Assuming node "clock" is an undefined clock

Complete Simulation • 4,000,000 x 250 ns x 100 = 100 seconds • 1 second simulation on 2 GHz Pentium 4 with ½ Gigabytes of memory was 52 minutes • 100 seconds would be 5200 minutes = 3.6 Days • Drop LPM_COUNTER module from 4,000,000 to 4 for a few second simulation

One-Hundred Second Timer • Counts from 00 to 99 in one second intervals • Rolls over from 99 back to 00

Unused Pins as Tri-State Inputs • Select “Assignments” • Select “Device” • Select “Device & Pin Options” • Select “Unused Pins” Tab • Select “As inputs, tri-stated” • OK

Pre-Lab • 3-Bit Shift Register State table • Waveforms for 3-Bit Shift Register