3.1 位逻辑指令 Bit Logic Instructions

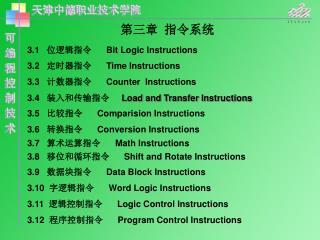

第三章 指令系统. 3.1 位逻辑指令 Bit Logic Instructions. 3.2 定时器指令 Time Instructions. 3.3 计数器指令 Counter Instructions. 3.4 装入和传输指令 Load and Transfer Instructions. 3.5 比较指令 Comparision Instructions. 3.6 转换指令 Conversion Instructions.

3.1 位逻辑指令 Bit Logic Instructions

E N D

Presentation Transcript

第三章 指令系统 3.1 位逻辑指令 Bit Logic Instructions 3.2 定时器指令 Time Instructions 3.3 计数器指令 Counter Instructions 3.4 装入和传输指令 Load and Transfer Instructions 3.5 比较指令 Comparision Instructions 3.6 转换指令 Conversion Instructions 3.7 算术运算指令 Math Instructions 3.8 移位和循环指令 Shift and Rotate Instructions 3.9 数据块指令 Data Block Instructions 3.10 字逻辑指令 Word Logic Instructions 3.11 逻辑控制指令 Logic Control Instructions 3.12 程序控制指令 Program Control Instructions

3.1 位逻辑指令 Bit Logic Instructions 3.1.1 基本位逻辑指令 3.1.2 置位/复位指令 3.1.3 边沿信号识别指令 3.1.4 RLO 置位、清零、保存指令

3.1.1 基本位逻辑指令 A And 逻辑“与” AN And Not 逻辑“与非” O Or 逻辑“或” ON Or Not 逻辑“或非” X Exclusive Or 逻辑“异或” XN Exclusive Or Not 逻辑“异或非” = Assign 赋值指令 NOT Negate RLO RLO取反 SET Set RLO (=1) RLO=1 CLR Clear RLO (=0) RLO=0

梯形图LAD表示的基本位逻辑指令 ---| |--- 常开触点 ---|/|--- 常闭触点 ---(SAVE) 将RLO的状态保存到BR XOR 逻辑“异或” ---( ) 输出线圈 ---( # )--- 中间标志输出 ---|NOT|--- RLO取反

1.逻辑“与”操作 功能图(FBD) 梯形图(LAD)语言如下: 语句表(STL)语言如下: A I 0.0 A I 0.1 = Q 4.0

2.逻辑“或”操作 功能图(FBD)语言如下: 梯形图(LAD)语言如下: 语句表(STL)语言如下: O I 0.0 O I 0.1 = Q 4.0

3.逻辑“异或”操作 功能图(FBD)语言如下: 梯形图(LAD)语言如下: 语句表(STL)语言如下: X I 0.0 X I 0.2 = Q 3.1

4.逻辑取反操作 功能图(FBD)语言如下: 梯形图(LAD)语言如下: ---|NOT|--- 语句表(STL)语言如下: X I 0.0 X I 0.2 = Q 3.1

5.中间输出符号 6.位逻辑操作规则: 位逻辑指令的运算规则:“先与后或”。

3.1.2置位/复位指令 语句表STL表示的置位/复位指令 R Reset 复位指令 S Set 置位指令 梯形图LAD表示的置位/复位指令 ---( S ) Set Coil 线圈置位指令 ---( R ) Reset Coil 线圈复位指令 SR 复位优先型双稳态触发器指令 RS 置位优先型双稳态触发器指令

1.置位/复位线圈指令语句 功能图(FBD)语言如下: 梯形图(LAD)语言如下:

2.置位/复位双稳态触发器指令 置位优先型RS触发器: 复位优先型RS触发器:

3.1.3边沿信号识别指令 1.RLO边沿信号识别指令 上升沿信号识别指令

2.触点边沿信号识别指令 触点上升沿信号识别指令 触点下降沿信号识别指令

3.1.4 RLO 置位、清零、保存指令 置位指令 符号: SET 功能: RLO = 1 复位指令 符号: CLR 功能: RLO = 0 RLO保存指令 符号: SAVE 功能: (RLO) → BR

3.2 定时器指令 Time Instructions 3.2.1 定时器的结构 3.2.2 脉冲定时器 3.2.3 定时器再启动指令FR 3.2.4 扩展脉冲定时器 3.2.5 接通延时定时器 3.2.6 保持型接通延时定时器 3.2.7 关断延时定时器

A I 2.0 FR T1 A I 2.1 L S5T#10s SP T1 A I 2.2 R T1 A T1 = Q4.0 3. 2. 3 定时器再启动指令FR

3.3 计数器指令 Counter Instructions 3.3.1 计数器的结构 3.3.2 计数器再启动指令FR

可逆计数器 加计数器 减计数器 端子说明: CU —加计数输入 CD —减计数输入 S —预置输入 PV —设置计数初值 R —复位输入 Q — 计数器状态输出 CV —当前计数值输出(十六进制格式) BCD—当前计数值输出(BCD码格式)

A I 0.0 CU C 10 A I 0.1 CD C 10 A I 0.2 S C 10 L C#55 A I 0.3 R C 10 A C 10 = Q 4.0

3.4 装入和传输指令 3.4.1装入和传输指令 3.4.2 状态字 3.4.3 读取或传送状态字 3.4.4 装入时间值或计数值 3.4.5地址寄存器装入和传送 3.4.6.传送指令

3.4.1装入和传输指令 L 通用装入指令 L STW 将状态字寄存器的内容装入到累加器1 LAR1 AR2 将地址寄存器2的内容装入到地址寄存 器1 LAR1 <D> 将32位的长整数装入到地址寄存器1 LAR1 将累加器1的内容装入到地址寄存器1 LAR2 <D> 将32位的长整数装入到地址寄存器2 LAR2 将累加器1的内容装入到地址寄存器2

T 通用传输指令 T STW 将累加器1的内容传输到状态字寄存器 TAR1 AR2 将地址寄存器1的内容传输到地址寄存 器2 TAR1 <D> 将地址寄存器1的内容传输到目的单元 (32位) TAR2 <D> 将地址寄存器2的内容传输到目的单元(32位) TAR1 将地址寄存器1的内容传输到累加器1 TAR2 将地址寄存器1的内容传输到累加器2 CAR 交换地址寄存器的1的内容和地址寄存 器2的内容交换

3.4.2 状态字 1. 首位检测位(FC) 2. 逻辑操作结果(RLO) 3. 状态位(STA) 4. 或位(OR) 5. 溢出位(OV) 6. 溢出状态保持位(OS) 7. 条件码1(CC1)和条件码0(CC0) 8.二进制结果位(BR)

3.4.3 读取或传送状态字 LSTW 状态字中0—8位装入累加器1 中,累加器9—31位被清0 TSTW 将累加器1中的内容传送到状 态字中 • 注:对 S7-300系列的CPU, LSTW不对状态字中的SC、STA、OR位进行操作,仅将状态字中的1,4,5,6,7位装入累加器1的对应位。

3.4.4 装入时间值或计数值 L T1 将定时器T1中二进制格式的时间值 直接装入累加器1的低字中 LC T1 将定时器T1中的时间值和时基以 BCD码格式装入累加器1 低字中 L C1 将计数器C1中计数值以二进制格式 装入累加器1的低字中 LC C1 将计数器C1中的计数值以BCD码 格式装入累加器1低字中

3.4.5地址寄存器装入和传送 LAR1 将操作数的内容装入地址寄存器1; LAR2 将操作数的内容装入地址寄存器2; TAR1 将ARl的内容传送给存储区或 AR2; TAR2 将AR2的内容传送给存储区或 AR2; CAR 交换ARl和AR2的内容

3.4.6.传送指令 FBD符号: 端子说明: EN ——允许输入端 IN —— 源数据输入端 OUT —— 目的操作数输出 ENO —— 允许输出端

3.5.比较指令 Comparision Instructions 3.5.1比较两个整数或长整数 3.5.2比较两个实数

3.6. 转换指令 Conversion Instructions 3.6.1BCD和整数间的转换 3.6.2 实数和长整数间的转换 3.6.3数的取反取负 3.6.4 字节交换指令

3.6.1BCD和整数间的转换 BTI 3位BCD码数转换为16位整数 BTD 7位BCD码数转换为32位整数 ITB 16位整数转换3位BCD码数 ITD 16位整数转换为32位整数 DTB 32位整数转换为7位BCD码数 DTR 32位整数转换为32位浮点数

BTD 将累加器1低字中的7位BCD码数 转换为32位整数 ITB 将累加器1低字中的16位整数转换 为3位BCD码数 例3.6.2 L MW 10 ITB T MW20

例3.6.1 L MW 10 BTI T MW20

例3.6.2 L MW 10 ITB T MW20

例3.6.3 L MW 10 ITB T MW20