ISA Instructions (logical + procedure call)

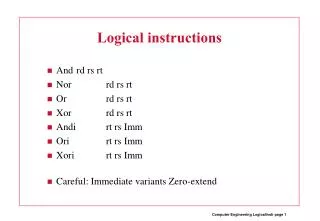

ISA Instructions (logical + procedure call). Chapter 2. Logical operations. Shift left Example: sll $t2,$so,4 Reg t2 = $so << 4 Shift right Example: srl $t2,$so,4 Reg t2 = $so >> 4 Bit-wise AND Example: and $t0,$t1, $t2 Reg t0 = reg t1 & reg t2 Bit-wise OR

ISA Instructions (logical + procedure call)

E N D

Presentation Transcript

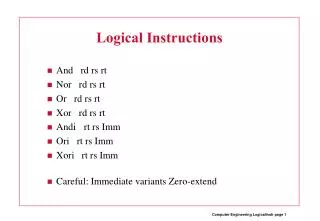

Logical operations • Shift left • Example: sll $t2,$so,4 • Reg t2 = $so << 4 • Shift right • Example: srl $t2,$so,4 • Reg t2 = $so >> 4 • Bit-wise AND • Example: and $t0,$t1, $t2 • Reg t0 = reg t1 & reg t2 • Bit-wise OR • Example: or $t0,$t1,$t2 • Reg $t0 = $t1 | $t2

Instructions for Selection (if..else) • If (i == j) then f = g + h; else f = g – h; bne $s3,$s4, else add $s0,$s1,$s2 j done else: sub $s0,$s1,$s2 done:

Instructions for Iteration (while) • while (save[i] == k) • i = i + 1; Let i be in reg $s3 Let k be in reg $s5 Let $t1 have the address of Save array element Loop: sll $t1,$s3,2 add $t1,$t1$s6 lw $t0,0($t1) bne $t0,$s5,Exit addi $s3,$s3,1 j Loop

Compiling C procedures int leaf_example (int g, int h, int i, int j) { int f; f = (g + h) – (i + j); return f; } How do you pass the parameters? How does compiler transport the parameters?

Passing Parameters/arguments Special registers for arguments: a0, a1, a2, a3 Save temp register on the stack Perform operations And return value Restore values stored on the stack Jump back to return address

Steps in Execution of a Procedure • Place parameters in a place where procedures can access them • Transfer control to the procedure • Acquire the storage resources needed for the procedure • Perform the desired task • Place the result value in a place where the calling program can access it • Return control to the point of origin, since a procedure can be called from several points in a program

Register Mapping – Ahah! R0 (r0) = 00000000 R1 (at) = 00000000 R2 (v0) = 00000000 R3 (v1) = 00000000 R4 (a0) = 00000000 R5 (a1) = 00000000 R6 (a2) = 00000000 R7 (a3) = 00000000 R8 (t0) = 00000000 R9 (t1) = 00000000 R10 (t2) = 00000000 R11 (t3) = 00000000 R12 (t4) = 00000000 R13 (t5) = 00000000 R14 (t6) = 00000000 R15 (t7) = 00000000 R16 (s0) = 00000000 R17 (s1) = 00000000 R18 (s2) = 00000000 R19 (s3) = 00000000 R20 (s4) = 00000000 R21 (s5) = 00000000 R22 (s6) = 00000000 R23 (s7) = 00000000 R24 (t8) = 00000000 R25 (t9) = 00000000 R26 (k0) = 00000000 R27 (k1) = 00000000 R28 (gp) = 10008000 R29 (sp) = 7fffeffc R30 (s8) = 00000000 R31 (ra) = 00000000

Procedure Call Conventions • $a0-$a3 : four argument registers in which to pass parameters • $vo-$v1: two value registers in which to return values • $ra: one return address register to return to point of origin of the call • MIPS assembly language also has a special instruction jal (jump and link) that saves the return address in $ra before transferring control to the procedure. • Eg: jal ProcedureAddress • Another instruction “jr” transfers control back to the called location. • Eg. jr $ra

Using the Stack “automatic storage” • Automatic store for “workspace” and temporary registers. • Use the stack: • Use the stack pointer to access stack; • Remember stack operates on LIFO • Also note that $ZERO is a convenience register that stores the value 0 (check your green sheet attached to your textbook) • Now we are ready to translate the procedure:

Translating the procedure int leaf_example (int g, int h, int i, int j) { int f; f = (g + h) – (i + j); return f; } • Parameters g, h, i, j will be stored in argument registers: $a0,$a1,$a2,$a3 before the call • Once inside we plan to use $s0, $t0, $t1; so we need save their values on the stack; • Then use them to compute (g+h), (i+j) and f

MIPS code addi $sp,$sp,-12 # make room on the stack sw $t1,8($sp) # save the temp registers sw $t0,4($sp) sw $so,o($sp) add $to,$ao,$a1 # t0 g + h add $t1,$a2,$a3 # t1 i + j sub $so,$t0,$t1 # f = t0 – t1 add $v0,$so,$zero # returns f ($vo = $s0 + 0) lw $s0,0(sp) # restore saved values into temp registers from stack lw $t0,4(sp) lw $t1,8(sp) addi $sp,$sp,12 jr $ra # jump back to the return address

Allocating Space on Stack • Stack is used to save and restore registers when calling a procedure • It may also be used to store return address • It may be used to store arguments • It may be used to store local arrays and data • The segment of the stack containing a procedure’s saved registers and local variables is called “procedure frame” or “activation record” • A frame pointer ($fp) points to first word of the frame of a procedure.

Stack and frame pointers before after during fp fp sp sp fp Saved arguments Saved return addr Saved regs . Locals arrays & structures sp

Delayed Branches Branch: Execute Inst Fetch Dcd & Op Fetch execute successor even if branch taken! Dcd & Op Fetch Execute Inst Fetch Inst Fetch Then branch target or continue Single delay slot impacts the critical path • add r3, r1, r2 • sub r4, r4, 1 • bz r4, LL • NOP • ... • LL: add rd, ... • Compiler can fill a single delay slot with a useful instruction 50% of the time. • try to move down from above jump • move up from target, if safe

Delayed Branches • li r3, #7 • sub r4, r4, 1 • bz r4, LL • subi r6, r6, 2 • LL: slt r1, r3, r5 • li r3, #7 • sub r4, r4, 1 • bz r4, LL • nop • LL: slt r1, r3, r5 subi r6, r6, 2 compiler

Branch and Pipelines Time • li r3, #7 execute • sub r4, r4, 1 ifetch execute • bz r4, LL ifetch execute Branch • subi r6, r6, 2 Delay Slot ifetch execute LL: slt r1, r3, r5 ifetch execute Branch Target By the end of Branch instruction, the CPU knows whether or not the branch will take place. However, it will have fetched the next instruction by then, regardless of whether or not a branch will be taken. Why not execute it?

Putting it all together • Sort procedure void sort (int v[], int n) { int i, j; for (i = 0; i < n; i = i+1) { // outer loop for (j = i - 1; j >= 0 && v[j] > v[j+1]; j = j-1){ swap(v, j); } } }