Exploring Algorithms in Column-Matching BIST Method for Enhanced Circuit Testing

40 likes | 170 Vues

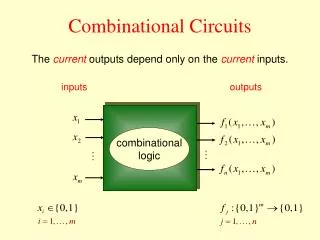

This paper presents an in-depth survey of the algorithms implemented in the Column-Matching Built-In Self-Test (BIST) method designed for combinational circuits. It outlines the Mixed-Mode BIST structure, detailing two distinct test phases: pseudorandom and deterministic testing. Core principles and decoder logic are explored, focusing on matching operations within the C-Matrix and T-Matrix. The report concludes with methods for column selection and matching strategies, emphasizing the NP-hard nature of final assignments and various heuristic techniques.

Exploring Algorithms in Column-Matching BIST Method for Enhanced Circuit Testing

E N D

Presentation Transcript

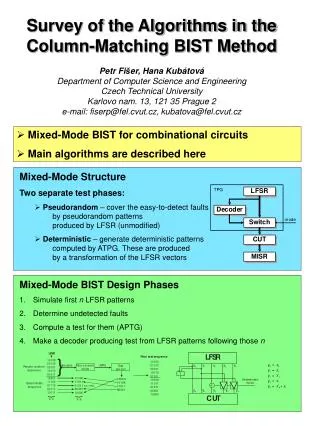

Survey of the Algorithms in the Column-Matching BIST MethodPetr Fišer, Hana KubátováDepartment of Computer Science and EngineeringCzech Technical UniversityKarlovo nam. 13, 121 35 Prague 2e-mail: fiserp@fel.cvut.cz, kubatova@fel.cvut.cz • Mixed-Mode BIST for combinational circuits • Main algorithms are described here • Mixed-Mode Structure • Two separate test phases: • Pseudorandom – cover the easy-to-detect faults by pseudorandom patterns produced by LFSR (unmodified) • Deterministic – generate deterministic patterns computed by ATPG. These are produced by a transformation of the LFSR vectors • Mixed-Mode BIST Design Phases • Simulate first n LFSR patterns • Determine undetected faults • Compute a test for them (APTG) • Make a decoder producing test from LFSR patterns following those n

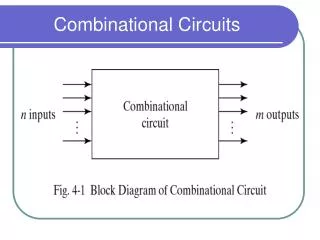

Column - Matching • The Decoder = purely combinational circuit • It is being designed using the Column-Matching Algorithm • Input: • The C-Matrix = the LFSR code words • The T-Matrix = the deterministic test patterns • Output: • The Decoder logic transforming some of the C-Matrix rows to all T-Matrix rows – makes an assignment of rows • Principles of the Method • We try to implement as many Decoder outputs as simple wires - without any combinational logic • If we reorder the T-matrix vectors so that some test columns are equal to the LFSR columns, the outputs of the decoder described by these columns will be implemented as wires (we call itmatches) • No output decoder is needed for matched columns • Remaining outputs must be synthesized by some Boolean minimizer (ESPRESSO, BOOM) • Direct Matches • If i-th C-Matrix column is matched with j-th T-Matrix column, no decoder logic is needed, however, the MUX has to be present in the Switch • But - if i-th C-Matrix column is matched with i-th T-Matrix column, no MUX is needed – really just a wire! – we call it adirect match • Negative Matches • If i-th C-Matrix column is matched with j-th T-Matrix column, but having opposite values, no decoder is needed, switch = MUX+NOT • If i-th C-Matrix column is matched with i-th T-Matrix column, but having opposite values, no decoder is needed, switch = XOR • Negative (direct) matches

How to Do It? • How to select the columns to be matched? • It is of a key importance. But NP-hard some heuristic needed • In fact – when # of C-Matrix columns >> # of T-matrix columns, almost any match is possible, until some threshold we do it at random • What to do after a match is found? • The possible assignments of the rows have to be restricted. Two methods: • Decomposition into Set Systems • Initially, each of the test vectors might be assigned to any of the LFSR vectors. When an ith T-matrix column is matched with j-th C-matrix column, all the values in these columns have to be equal. Thus, both sets of the test and LFSR vectors have to be divided into halves – the halves with the “1” and “0” values in the matched columns. Vectors belonging to the sets with equal values can be matched with each other, the others not each match = one division, until one set is empty. Then the matching ends. • The final assignment of rows is easy – to each T-matrix row select one at random. • Blocking Matrix • Set system approach is not suitable for tests with don’t cares – the divided matrices must be repeatedly duplicated here – slow • Blocking matrix B = binary matrix, B[r, s] = 1 when r-th C-Matrix row can be assigned to the s-th T-Matrix row • Initially, all cells contain “1”s • After each match, the B matrix is “pruned” • The final assignment is not easy – NP-hard. If c1 is assigned to t1 – OK But if c1 is assigned to t4 – no solution

B-Matrix Assignment Algorithms Note: All the T-Matrix rows have to be assigned to some C-Matrix rows all B-Matrix columns have to be covered by rows Not a standard CP! One row covers only one column! Methods • Random Randomly select one column, then randomly select one row – just for comparison • LCLR (Least Column - Least Row) heuristic Select column with the least number of “1”s (i.e., with a small chance to be covered) and select an appropriate row with a least number of 1s to it (i.e., for other columns the most “useless” one) • Scoring matrix based heuristic Like LCLR, however more sophisticated – computes scoring matrix based on those two frequencies of 1s. Good, but slow. Comparison with Other Methods Acknowledgement This research was supported by a grant GA 102/03/0672 and MSM 212300014