CHAPTER 13 REDUCED INSTRUCTION SET COMPUTERS (RISC)

CHAPTER 13 REDUCED INSTRUCTION SET COMPUTERS (RISC). CSNB123 coMPUTER oRGANIZATION. Expected Course Outcome. RISC. New type processor architecture. RISC: Key Features. Large number of registers or the use of a compiler that optimizes register usage A limited and simple instruction set

CHAPTER 13 REDUCED INSTRUCTION SET COMPUTERS (RISC)

E N D

Presentation Transcript

CHAPTER 13REDUCED INSTRUCTION SET COMPUTERS (RISC) CSNB123 coMPUTERoRGANIZATION Systems and Networking

Expected Course Outcome Systems and Networking

RISC • New type processor architecture Systems and Networking

RISC: Key Features • Large number of registers or the use of a compiler that optimizes register usage • A limited and simple instruction set • Emphasis on optimizing the instruction pipeline Systems and Networking

Characteristic of Some CISCs, RISCs, and Superscalar Processors Systems and Networking

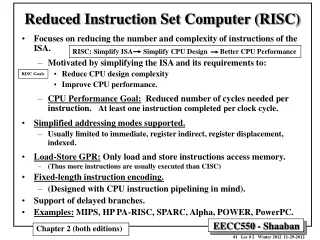

CISC - Complex Instruction Set Computer • Before RISC • Cost of hardware drop, the relative cost of software rise • More powerful and complex HLL been introduced • The HLL allow the programmer to express algorithms more concisely Systems and Networking

CISC - Complex Instruction Set Computer Problem: Semantic gap • The different between the operations provided in HLLs and those provided in computer architecture • Symptom; • Inefficient of execution • Excessive machine program size • Compiler complexity Systems and Networking

Intension of CISC • Ease the task of the computer writer • Improve execution efficiency because complex sequences of operations can be implemented in microcode • Provide support for even more complex and sophisticated HLLs Systems and Networking

Importance of RISC • Need simpler architecture to support HLL • To understand the importance to have RISC need to look at the instruction execution characteristics; • Operations performed = these determine the functions to be performed by the processor and its interaction with memory • Operands used = the types of operands and the frequency of their use determine the memory organization for storing them and the addressing modes for accessing them • Execution sequencing = this determines the control and pipeline organization. Systems and Networking

Importance of RISC (Cont.) • Summary; • Need quick access to operands • There are large proportion of assignment statements in HLL program • Need register storage for faster computation Systems and Networking

Importance of RISC (Cont.) - Register • Faster than main memory and cache • Register file • Physically small, located on the same chip as the ALU and control unit and employ much shorter addresses than addresses for cache and memory Systems and Networking

Importance of RISC (Cont.) - Register • Strategy: allow most frequently accessed operands to be kept in registers and to minimize register-memory operations in RISC machine • Software based • Hardware based Systems and Networking

Importance of RISC (Cont.) - Register Software Based Hardware Based Use more registers so that more variables can be held in registers for longer period of time • Rely on the compiler to maximize register usage • The compiler will attempt to allocate register to those variables that will be used the most in a given period • Need to use a sophisticated program program-analysis algorithms Systems and Networking

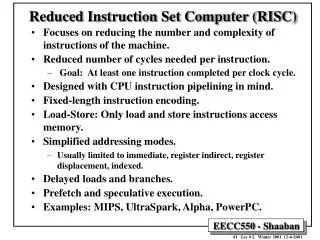

Characteristic of RISC • One instruction per cycle • A machine cycle is defined to be the time it takes to fetch two operands from registers • Perform an ALU operation • Store the result in a register • RISC should not be complex as CISC • Machine instructions can be hardwired • Instruction operate faster • Register-to-register operations • Most operation should be R-to-R with only simple LOAD and STORE operations accessing memory • This make the instruction set simple • CISC include memory-to-memory and mixed register /memory operations Systems and Networking

Characteristic of RISC (Cont.) • Simple addressing modes • RISC used simple register addressing • Simple instruction formats • Instruction length is fixed • The opcode are fixed • The benefit is that, opcode decoding and register operand accessing can occur simultaneously Systems and Networking

Additional Reference • William Stallings, Computer Organization and Architecture: Designing for Performance, 8th. Edition, Prentice-Hall Inc., 2010 Systems and Networking

This teaching material is belongs to Systems and Networking Department College of Information Technology UniversitiTenagaNasional (UNITEN) Malaysia 2014 Systems and Networking