Reduced Instruction Set Computing

Reduced Instruction Set Computing. Tun,Aung Kyaw Cs-147. Overview. RISC Rationale (Reduced Instruction Set Computers) RISC Instruction Sets Instruction Pipelines and Register Windows Instruction Pipelines Conflicts RISC vs. CISC (Complex Instruction Set computers). RISC Rationale.

Reduced Instruction Set Computing

E N D

Presentation Transcript

Reduced Instruction Set Computing Tun,Aung Kyaw Cs-147

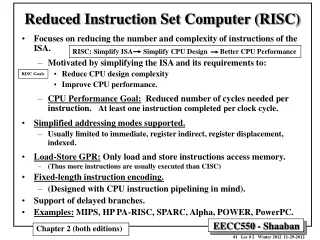

Overview • RISC Rationale (Reduced Instruction Set Computers) • RISC Instruction Sets • Instruction Pipelines and Register Windows • Instruction Pipelines Conflicts • RISC vs. CISC (Complex Instruction Set computers)

RISC Rationale • The greater the number of instruction in and instruction set, the larger the propagation delay is within the CPU eg. 4- to -16 decoder and- 5 to-32 decoder the second one requires more time to generate its output than the first one ( first one reduces the maximum clock rate of CPU)

Reasons of Reducing the time • Allow the CPU to run at a higher frequency • Perform each instruction more quickly

Instruction Requirements • 1) Fetch • 2)Decode • 3)Execute

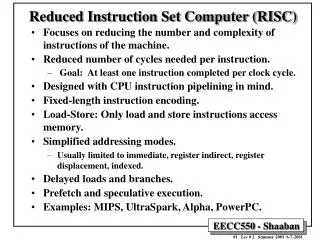

Characteristics of RISC Processors • Reduced Instruction set size • Less complex Instructions • Fixed Length Instruction • Limited Loading and Sorting Instructions Access memory • Fewer Addressing Modes • Instruction Pipeline

(Continued) • Large number of Registers • Hardwired Control Unit • Delay loads and Branches • Speculative Execution of Instructions • Optimizing Compiler • Separate instruction and Data Streams

Fixed Length Instruction • In RISC processors, • Every instruction has the same size • Eg. Immediate mode instruction might include an 8 bit operand • Other instructions might use these 8 bits for opcodes or address information

Limited Loading and Sorting Instructions Access Memory • RISC processor limit interaction with memory to loading and sorting data • If a value from memory is to be ANDed with the accumulator, • the CPU first loads the value into a register • Then performs the and operation

Fewer Addressing Modes • Allow only a few addressing modes that can be processed quickly • (register indirect and relative modes)

Instruction Pipeline • Like an assembly Line • Worked on simultaneously and differently • One instruction is executed while the next is being decoded • Its operands are being loaded • Next instruction is being Fetched • CPU executes one instruction per clock cycle

Large Number of Registers • Why is it good? • Allows CPU to store many operands internally • CPU fetches them from the register rather than from the memory • Reduces the access time • Less space for control logic

Hardwired Control • Hardwired control unit can run at a higher clock frequency than its corresponding microcoded control unit • ease of modification

Delayed Loads and Branches • RISC use delay loads and delayed branches to avoid wasting time • it can avoid branch instructions or consecutive instructions which was caused by Instruction Pipeline

Speculative Execution of Instructions • The CPU executes the instruction but doesn’t store its result • The result is stored if the CPU is to be executed the instruction • otherwise, the result is discarded

Optimizing Compiler • It can arrange instructions to facilitate delayed loads and branches • And assign operands to registers • Fewer instructions make RISC processor to design an optimizing compiler

Separating Instruction and Data Streams • The instruction pipeline may need to access instructions and operands from memory simultaneously • Separating the instruction and data streams helps to avoid memory access conflicts

RISC Instruction Set • RISC processors are reduced, or smaller in size than compare to CISC processors • each instruction is executed in a single clock circle • Note: it is important not to reduce the set too much because sometimes removing instruction would decrease the system performance

Types of Instructions • Basic types of instructions include • 1) data move (load, store,and register remove) • 2) ALU (arithmetic,logic,and shift) • 3) Branch Instructions

Data Types • Generally RISC CPU operate integer and floating point • Don’t include instructions to manipulate character strings or data types directly

Notes • In RISC processor,every Instruction must have the same number of bits regardless of format types • CPU must be able to access each instruction in a single memory-read operation • it will make easier in pipelining • eg. using different formats used by 32 bit SPARC CPU

Instruction Set (continued) • Instruction set of RISC processor access memory using load and store instruction • several different types of load • LB (instruction loads a byte(8 bits) of data) • LH(instruction loads half word(16 bits)of data) • LW(instruction loads a word(32 bits)of data)

Characteristics of RISC • RISC contain fewer addressing modes • common things is address can be computed in a single clock cycle

Instruction Pipelines and Register Window • Two techniques commonly use in RISC processors to improve performance • 1) RISC CPU uses pipelined instruction units to break down the fetch-decode-execute procedure • process other techniques in parallel • 2)Incorporation of large numbers of registers within the CPU

Instruction Pipelines • Similar to a manufacturing assembly line • Pipe Instruction works the same way as assembly line process the product

Instruction Pipelines (Continued) • First stage Fetches the instructions from the memory • Second stage Decodes the instructions and Fetches any required operands • Third stage executes the instruction • Fourth stage stores the result

(Continued) • Each stage processes instruction simultaneously • this allows the CPU to execute the instruction per clock cycle

RISC&Stages • The first RISC computer uses a four-stages instruction pipeline

Example • The flow of instruction though each pipeline • One instruction per clock cycle

Pipeline control unit & Advantages • Reduce hardware requirements of the Pipeline • each state performs only a portion of the fetch-decode-and execute process,no stage needs to incorporate the hardware of a complete control unit • eg.Instruction-fetch stage need to read an instruction from the memory (doesn’t need decode or execute instructions)

(Continued) • Second advantage of instructions pipelines is the reduced complexity of the memory interface • Pipeline achieves its maximum performance when all stages have the same delay

Register Windowing • In RISC CPU, always accessible registers are called Global Register • The remaining are windowed • only subset of the registers are accessible at any specific time

Instruction Pipeline conflicts • Two types of conflicts • 1) Data Conflicts: occur when the pipelines causes and incorrect data value to be used • 2)Branch Conflicts: occur when a branch statement results in incorrect instructions being executed

Data Conflicts • It occurs in a pipeline when one instruction stores a result in a register and another instruction uses that value as an operand • occurs when one instruction stores a result in a register and subsequent instruction reads the contents of that register before first instruction has stored its result

Branch Conflicts • Occurs within Branch or Jump statements in RISC instruction pipeline • it does not cause incorrect data values to be used • but it the CPU to execute instructions at a times when they should not be executed

RISC vs.CISC • RISC processors have fewer and simpler instruction than CISC processors • this allow RISC to run at higher clock frequencies than CISC processors • RISC reduces the amount of space needed on the chip than CISC • RISC are less complex than CISC

Conclusion • RISC characteristics • RISC Instruction Sets • Instruction Pipelines • Register Windows • Data conflicts • Branch conflicts • RISC vs. CISC

Thanks You & • “Happy Thanksgivings”