Instruction Set Design

Instruction Set Design. CE 140 A1/A2 30 June 2003. Six-Level Computer. PROBLEM-ORIENTED LANGUAGE LEVEL. Level 5. ASSEMBLY LANGUAGE LEVEL. Level 4. OPERATING SYSTEM MACHINE LEVEL. Level 3. IS DESIGN. INSTRUCTION SET ARCHITECTURE LEVEL. Level 2. MICROARCHITECTURE LEVEL. Level 1.

Instruction Set Design

E N D

Presentation Transcript

Instruction Set Design CE 140 A1/A2 30 June 2003

Six-Level Computer PROBLEM-ORIENTED LANGUAGE LEVEL Level 5 ASSEMBLY LANGUAGE LEVEL Level 4 OPERATING SYSTEM MACHINE LEVEL Level 3 IS DESIGN INSTRUCTION SET ARCHITECTURE LEVEL Level 2 MICROARCHITECTURE LEVEL Level 1 DIGITAL LOGIC LEVEL Level 0

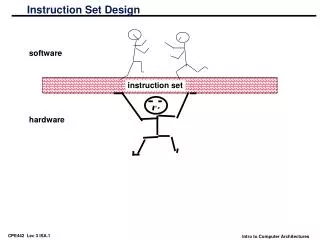

Instruction Set Architecture • Interface between hardware and software (compilers) • High-level languages are translated to ISA level • Hardware is built to execute ISA-level programs directly

ISA Design Process • Architect will talk to compiler writers and hardware engineers • Is it cost-effective? • Can it be used? • Output: a perfectly optimized ISA that satisfies both compiler writers and hardware engineers NOT ALWAYS

More ISA Design Requirements • “Is it compatible with the predecessor?” • “Can I run my old operating system on it?” • “Will it run all my existing application programs unmodified?” • Constraint: Backward compatibility

What makes a good ISA? • Hardware engineers: Instruction set that can be impemented efficiently in current and future technologies • Compiler writers: Clean target for compiled code

ISA Level • How machine appears to machine language programmer • Memory Model • Registers • Data types • Instructions

Memory Model • Big Endian or Little Endian • Alignment requirements • Address space

Registers • Special-purpose registers • PC, SP • General-purpose registers • Variables, results, temporary storage • Fast access • Flags register or Program Status Word (PSW)

Instructions • LOAD, STORE, MOVE • Arithmetic instructions • Logical instructions • Boolean instructions • Comparing, branching

Data types • Hardware supported data types • Integers (signed and unsigned) • Floating-point numbers • BCD • Strings • Boolean values

Instruction Format • Instruction • Opcode • Addressing mode • Operands

Classifying ISAs • C = A + B

Design Critera for Instruction Formats • Size • Can accommodate all operations • Number of bits in the address field

Expanding Opcode • 16-bit instructions

Addressing Modes • Immediate Addressing • Direct Addressing • Register Addressing • Register Indirect Addressing • Indexed Addressing • Based-Index Addressing

Immediate Addressing • Operand is directly specified • Immediately fetched from memory with instruction • Can only specify constant • Range limited by size of field • Example: MOV DL, 21 • Stores the value 21 into DL

Direct Addressing • Operand is specified by giving its address • Constant memory location • Can be used for global variables • Example: MOV AL, [0200] • Stores the byte located at offset 0200 into AL

Register Addressing • Operand is specified by giving the register it is stored in • Examples: • MOV AX, BX

Register Indirect Addressing • Operand is specified by the register that contains operand’s address • Pointer • Example: MOV AX, [BX] • Store the word located at the address specified in BX into AX

Indexed Addressing • Useful in accessing elements of a data structure • Example: • MOV CX, 5 • ST: ADD AX, 0200[SI] • ADD SI, 2 • LOOP ST

Instruction Types • Data Movement Instructions • Dyadic Operations • Monadic Operations • Comparison and Conditional Branches • Procedure Call Instructions • Stack Instructions • Loop Control • Input/Output

Data Movement Instructions • Movement = Copy • Examples • MOV AX, BX • MOV AX, [0200] • MOV [0200], AX

Dyadic Operations • Combine two operands to produce a result • Arithmetic operations • Logic operations • Examples: • ADD AX, BX • AND AX, BX

Monadic Operations • Single operand • Arithmetic and Logic operations • Examples: • Shift - SAL • Rotate - ROL

Comparison and Conditional Branches • Allow testing data and alter the sequence of instructions based on the result • Branching • Uses flags register • Examples: • CMP – compare • JE – jump if equal

Stack Instructions • Allow stack operations • Stack – LIFO (Last In, First Out) • Examples • PUSH AX • PUSH BX • POP BX • POP AX

Procedure Call Instructions • Procedure/subroutine – group of instructions that can be called from several places in the program • Return address must be stored • Examples: • CALL • RET

Loop Control • Execute a group of instructions a fixed number of times • Involves a counter • Examples: • LOOP 0100

Input/Output • Access input and output ports • Examples: • IN AX, 378 • OUT 378, AX

Pentium II ISA • IA-32 • Full support for 8086 and 8088 programs

Pentium II Operating Modes • Real Mode – operates like a simple 8086/8088 • Virtual 8086 Mode – 8086/8088 programs run in an isolated environment • Protected Mode – larger address space, four privilege levels

Pentium II Addressing Modes • Immediate • Direct • Register • Register Indirect • Indexed

Pentium II ISA Issues • Few, different registers • Addressing modes are highly irregular • Ancient ISA Current technology suited for RISC ISA’s • Next Generation: • IA-64 - Intel’s 64-bit platform – not compatible with IA-32 • AMD64 – AMD’s 64-bit platform – compatible with x86