Current Status of CSC Trigger Elements – Quick Summary

Current Status of CSC Trigger Elements – Quick Summary. Jay Hauser, with many slides from Darin Acosta and Stan Durkin On-chamber Comparator ASICs for Cathodes (CFEB cards) – DONE. ALCT Anode Trigger – almost done (~90%) Peripheral-crate TMB Trigger Motherboard – pre-production prototypes

Current Status of CSC Trigger Elements – Quick Summary

E N D

Presentation Transcript

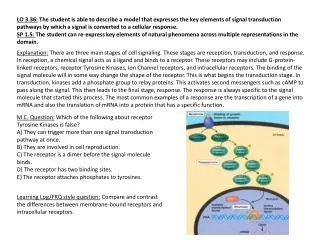

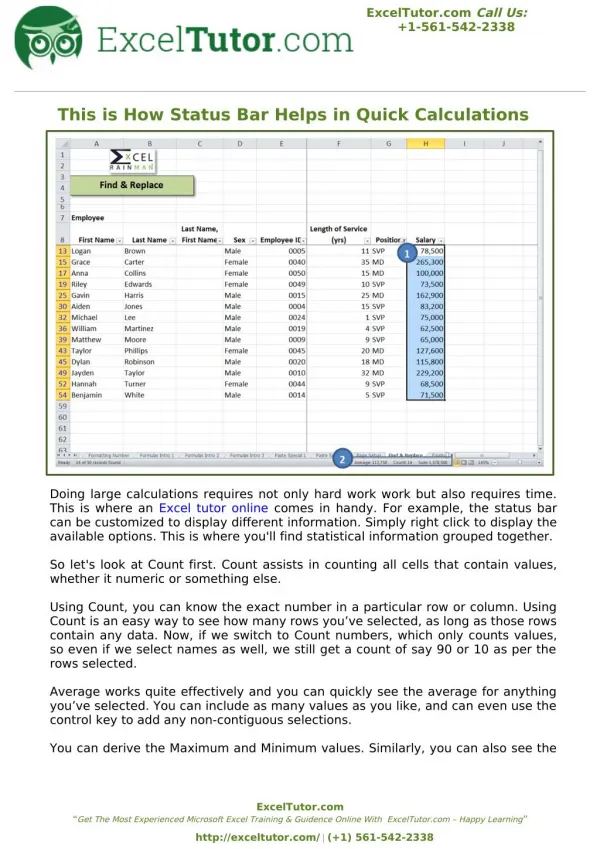

Current Status of CSC Trigger Elements – Quick Summary Jay Hauser, with many slides from Darin Acosta and Stan Durkin • On-chamber • Comparator ASICs for Cathodes (CFEB cards) – DONE. • ALCT Anode Trigger – almost done (~90%) • Peripheral-crate • TMB Trigger Motherboard – pre-production prototypes • MPC Muon Port Card – 2nd generation prototype • CCB Clock & Control Board – 2nd generation prototype • Track Finder crate in counting house • SP2002 Sector Processor – 2nd generation prototype • CSC Muon Sorter – 1st generation prototype • Backplane – 2nd generation prototype CMS Annual Review

D M B T M B D M B T M B D M B T M B D M B T M B D M B T M B C C B M P C T M B D M B T M B D M B T M B D M B T M B D M B C O N T R O L L E R 1 of 5 1 of 5 Cathode Front-end Board CFEB CFEB CFEB CFEB CFEB 1 of 2 1 of 24 ALCT LVDB Anode Front-end Board CSC CSC Muon Trigger Scheme EMU part: on-chamber nearing end of production, peripheral crate production > ESR in Nov. ‘03 TriDAS part: Second generation prototypes Muon Portcard (1) Trigger Motherboard (9) Clock Control Board Trigger Timing & Control DAQ Motherboard (9) Optical link Peripheral Crate on iron disk (1 of 60) Muon Sorter (1) Sector Processor (12) CSC Track-Finder Crate (1) Anode LCT Board In underground counting room On detector Trigger Primitives 3-D Track-Finding and Measurement CMS Annual Review

On-chamber CSC Trigger Electronics • Comparator ASICs – DONE. • Compare pulse heights from adjacent strips to find position of muon to ½-strip • 15000 16-channel ASICS on CFEB boards (OSU) • ALCT Boards – nearly DONE. • Finds tracks among anode hits, stores data for readout • 468+spares boards of 3 types (288-, 384-, 672-channel) CMS Annual Review

C C B D M B T M B D M B T M B D M B T M B D M B T M B D M B T M B M P C T M B D M B T M B D M B T M B D M B T M B D M B C O N T R O L L E R CSC Peripheral Crates in UXC55 Crate Controller DAQ Motherboard (DMB) TRIG Motherboard (TMB) Muon Port Card (MPC) Clock Control Board (CCB) CMS Annual Review

12 Used in CMS System SP2002 (Main Board) Receiver: Florida • Optical Transceivers • 16 x 1.6 Gbit/s Links VME/CCB FPGA TLK2501 Transceiver Data conversion: Phi Global LUT To/from custom GTLP back-plane Eta Global LUT Phi Local LUT Merged 3 SR2000s Front FPGA CMS Annual Review

SP Trigger Logic From SP2000 to SP2002 mezzanine card (5 manufactured) Florida Xilinx Virtex-2 XC2V4000~800 user I/O Performs track-finding logic and PT assignment CMS Annual Review

Sorts up to 36 muons from 12 SP’s and transmits best 4 to GMT Have 4 boards in hand, one stuffed (except for backplane interface) Sorter testing is in progress, will test with Track-Finder in the autumn Only 1 needed in CMS Muon Sorter Rice MEZZANINE CARD (same as SP design) LVDS DRIVERS AND SCSI-3 CONNECTORS GTLP BACKPLANE INTERFACE CMS Annual Review

CSC Test Beam Studies 2003 • First structured beam period May 23-June 1 • Trigger primitives tests were highly successful: • Verified peripheral crate electronics design for Nov. ESR • MPC-to-SP optical link data transfer unsuccessful (synch. problems) • Unstructured beam period June 13-28 • Improved low- and high-rate CLCT and TMB studies, angle scans • Second structured beam period Sept. 17-22 • Patches to fix optical link data transfer from MPC to SP • New readout shell program (fully OO software) CMS Annual Review

X5A Setup 2003 Time-structured Beam Test Setup TTC crate Trigger primitives DAQ Data PC Peripheral Crate 2 DMB, 2 TMB 1 CCB, 1 MPC FED crate 1 DDU Track finder Crate TRIDAS beam S1 S3 S2 CSC 2 CSC 1 CMS Annual Review

CSC Bunch ID From ALCT Timing • First, tune the ALCT data latching in 2 ns intervals (0-32ns) and maximize the single-BX fraction of events: • Then look at the BX distribution relative to BX from scintillator (L1A): • ALCT BX efficiency 98.7% CMS Annual Review

Chamber #1 CLCT 2,000 1,500 CLCT Rate (KHz) 1,000 data consistent with dead-time = 225 ns 500 0 0 500 1,000 1,500 2,000 2,500 3,000 Beam Intensity (KHz) Expected LCT rate at LHC < 25 KHz (ME1/1) CSC Trigger High Rate Tests CMS Annual Review

CSC Track Finder Test Sector Processor 2 CSCs • Successfully passed optical link loopback tests and MPCSP chain tests using 40 MHz crystal oscillator to drive system • MPCSP optical link tests failed at the structured beam tests in May 2003 (link errors every few ms) • Clock was derived from TTC system (mivivxrx) • Combined clock jitter presumably too large to drive optical links • PLL was not used to clean clock (i.e. QPLL was not available) CMS Annual Review

Additional 2003 Test Beam Results • (Later, unstructured beam period) • Very high efficiencies achieved • Highest trigger efficiency of 99.9% required low rate (few kHz) • Improved DAQ throughput allowed readout up to 80k full events per spill. Typical “run” is 1 or 2 spills. • Improved scans taken: • Logic scope read out on most data • HV scan • Comparator threshold scan • Pattern requirements scan • Angle scans fb CMS Annual Review

Sector Processor Clock Patch LVDS Repeater Delivers Multiplied Clock to Front FPGAs to Drive TLK2501 clock input VCXO and PLL added to clean synchronous clock • Voltage Controlled Crystal Oscillator PLL Patch • Low jitter Output • Cleans Backplane clock to drive SP logic • x2 BackPlane Clock supplies reference to TLK2501 CMS Annual Review

SP Patch Results • Eagerly awaiting QPLL chips from CERN CMS Annual Review

Preparation for Sept. 2003 Beam Test Cosmic ray test stand in Florida System brought to working order (everything now shipped to CERN) Scintillator Panels HV Supply CSCs TTCvx Periph Crate TF Crate MPC CCB SP TTCvi Dynatem TMB DDU CCB DMB SBS CMS Annual Review

Conclusions • The CSC system is in very good shape: • Chambers being mounted on disks at SX5 • Majority of the chambers already built and tested, including on-chamber electronics • Test beam showed that CSC peripheral crate electronics work very well under “battle conditions” • Of course, much work remains: • We especially need to validate the optical link clocking for MPC-SP data transfer • Production starts soon for peripheral crate electronics • Production planning will start soon for Track Finder (MPC, SP, MS) boards CMS Annual Review