TOPIC : Board-Level and System-Level DFT Approaches

100 likes | 398 Vues

UNIT 4 : Design for testability. TOPIC : Board-Level and System-Level DFT Approaches. Module 4.4 Board – level DFT approach. Board level DFT techniques. By a system we mean a collection of modules, such as PCBs, which consist of collections of ICs.

TOPIC : Board-Level and System-Level DFT Approaches

E N D

Presentation Transcript

UNIT 4 : Design for testability TOPIC : Board-Level and System-Level DFT Approaches Module 4.4 Board – level DFT approach

Board level DFT techniques • By a system we mean a collection of modules, such as PCBs, which consist of collections of ICs. • Many of the ad hoc DFT techniques referred to earlier such as scan can also be applied to the board level. • Primary system-level DFT approaches use existing functional • Busses, • scan paths, and • boundary scan.

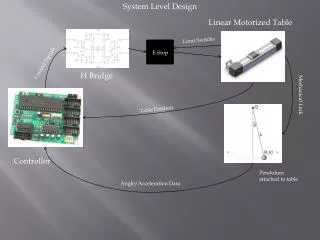

System-Level Busses • This DFT approach makes use of a module's or system's functional bus to control and observe signals during functional level testing. • A test and for maintenance processor, such as the ATE, appears as another element attached to the system's busses. • During testing, the ATE can take control of the system busses and test the system.

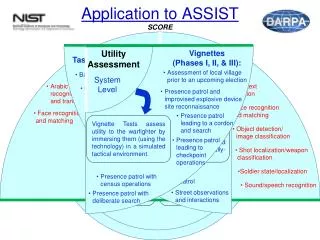

System-Level Scan Paths • Scan can be extended to the board and system levels. • The scan path of each chip on a board is interconnected in a daisy chain fashion to create one long scan path on each board. • The boards all share a common Sin, N/T and CLK input. Their Sout lines are wired-OR together. • The testing of such a system is under the control of a system-maintaince processor, which selects that board to be attached to the board-level scan line Sout as shown in next slide.

Scan applied to the system level Common Sin, N’/T and CLK