ECE 171 Digital Circuits Chapter 9 Hazards

690 likes | 947 Vues

Explore static and dynamic hazards, glitches, and their mitigations in digital circuit design. Learn about logic, function, and static-1 hazards with practical examples. Comprehensive insights on identifying and eliminating circuit hazards.

ECE 171 Digital Circuits Chapter 9 Hazards

E N D

Presentation Transcript

ECE 171Digital Circuits Chapter 9Hazards Herbert G. Mayer, PSU Status 4/1/2018 Copied with Permission from prof. Mark Faust @ PSU ECE

Syllabus Glitches and Hazards Static Logic Hazards Static Function Hazards Dynamic Hazards Hazard Exercises 1-5 Decoders Multiplexers References

Glitches and Hazards • So far we assumed: steady state of a circuit • Steady state is equivalent to having “waited” a long time for signals to settle • Long time meaning: more than 1 cycle for clocked-, or longer than signal propagation for un-clocked circuits • In practice, the actual time for a signal to propagate to the output gate can be long, and the time may depend on, which path that signal has taken • Depending on such paths, outputs may experience an unintended pulse, AKA glitch • Glitch means: though the steady state produces the correct signal, an opposite signal occurs momentarily

Glitches and Hazards • Hazard means the condition for a glitch exists • It doesn’t mean something unexpected actually occurs each time (think of road hazard) • Existence of hazard leaves open the possibility that a bad signal doesn’t occur at all during this execution • It means, the problem can occur, based on input signal combinations, and on actual signal path taken • The circuit designer must identify, whether hazards are acceptable or not • If hazards are not acceptable, a designer analyzes the circuit, introduces logic to eliminate all hazards, e.g. via consensus terms

Glitches and Hazards Glitch: Wrong signal in a circuit due to unequal delay paths; this is the manifestation of a hazard Logic Hazard: Is a glitch when one input changes. Can be removed by adding logic: AKA consensus terms Function Hazard: May cause glitch when two or more inputs change at once. Cannot generally be removed by adding logic Static Hazard: Occurs when output of the circuit is supposed to be constant. There are 2 kinds: unexpected 0, or unexpected 1 Dynamic Hazard: Occurs when output of the circuit changes unexpectedly more than once for a single input change Function and Logic Hazards can be Static or Dynamic

Glitches and Hazards • Definition: A static-1 hazard is an unexpected 0 output, generated by a pair of input combinations such that: a.) the two inputs differ by just 1 variable, b.) both combinations produce a 1 output signal, yet c.) an unwanted 0 signal occurs during the single input transition • Definition: A static-0 hazard is an unexpected 1 output, generated by a pair of input combinations such that: a.) the two inputs differ by just 1 variable, b.) both combinations produce a 0 output signal, yet c.) an unwanted 1 signal occurs during the single input transition • Definition: A dynamic hazard is the possibility of an unexpected change of the output signal more than once as a result of a single input signal change

Quick Check • 1.) Some circuit C1 contains a static-1 hazard. C1 is activated and after some defined time, it terminates. Does a problem occur in C1? • 2.) Some circuit C2 contains a static-0 hazard. C2 is activated and after some defined time, the circuit terminates with a glitch occurring; i.e. an unexpected ‘1’ signal was generated. Did an actual problem occur in C2’s output?

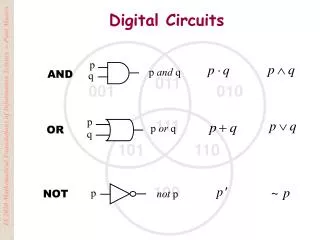

Reminder • SoP: Sum of Product terms • PoS: Product of Sum terms

Static Logic Hazards Single input changed. Resulting output should have remained constant: 1 in case(a). 0 in case(b). However, a glitch appeared before the output settled back to its correct level Two-level SoP circuits may see static-1 hazards Two-level PoS circuits may see static-0 hazards

Static-1 Logic Hazard Students draw minimized circuit in class, SoP form: And- and Or-gates OK, better even Nand-gates

1 1 0 1 1 1 Static-1 Logic Hazard Consider inputs ABC 111 time t1 110 time t2 NAND/NAND Implementation

Observe Carefully: • If first input at time t1 is: A B C = 1 1 1, the output F1 will be 1, due to nand-gate with inputs B C • Then at time t2 the input changes to A B C = 1 1 0 • Output F1 again is 1, due to nand-gate with inputs A C’, but the length (and thus the length of time) for the input path with signal C’ is longer, due to the inverter; may be critical! • In some instances that may be a sufficient delay to create a brief static 1 hazard, AKA 0 glitch • 1 hazard alluding to: signal should be 1 but isn’t • Static alluding to: signal should be 1 before, should be 1 after, but there is a wrong 0 value!

1 1 0 1 1 1 Static-1 Logic Hazard Consider inputs ABC 111 110 NAND/NAND Implementation

Countermeasure • To avoid this type of hazard: • With input transition 111 -> 110, output signal F1 should stay 1: was 1 initially, should remain 1 • Yet the “second 1” may arrive just a bit late: longer path • Add 3rd signal path (consensus term) that covers areas of 1s with further option to generate 1 signal: AB

Static-0 Hazard Implement a hazard-free circuit for the 0s of the previous function using NOR gates SoP Form for 0s: F1’ = . . . Students!! Students write F1( A, B, C ) in SoP form, for 0s

Static-0 Hazard Implement a hazard-free circuit for the 0s of the previous function using NOR gates SOP Form for 0s: • Hazard occurs at boundary of 2 terms, both of which deliver the same signal of interest, 0 here, at different times • Consensus term needed to deliver same signal, 0 here, if the other 2 terms may not “agree” about timing • To avoid a logic 1 glitch

Static-0 Hazard • Where is a critical boundary? • Look for: products grouped together! • Look for: logically adjacent terms in K-map • Add new term covering some ‘1’ (ones) of both, adjacent terms • Is redundant for signal-generation, but adds needed value that otherwise might get lost, due to glitch

Static-0 Hazard Students, which term is to be added? One that covers 0s, when 2 adjacent terms should be 0, but happen to become temporarily 1

Static-0 Hazard Implement a hazard-free circuit for the 0s of the previous function using NOR gates SOP Form for 0s Needed Cover Term Included

Static Function Hazards:Easy to Handle! The bad side-effect of multiple input signals changing and producing an unwanted signal cannotalways be removed by adding logic to the existing circuit; Solution: design new logic!

Hazard Example • Given the K-Map for function Haz() below: • Write function Haz() in SoP form • Identify where hazards exist • Devise a hazard-free function Haz’() equivalent to Haz()

Hazard Example • Assuming Haz() = a c’ + b c • The hazard arises between cells: a b c’ d and a b c d • Add new term a b d, so: Haz’() = a c’ + b c + a b d • Students, is that a correct fix? • Students, is that THE simplest form to avoid the hazard?

Hazard Example • Assuming function Haz() = a c’ + b c • The hazard arises between cells: a b c’ d and a b c d • Add simpler term a b, so: Haz’() = a c’ + b c + a b

Dynamic Hazards • Dynamic hazards occur in multi-level circuits with multiple paths, each having different delays from input to output • Do not occur in 2-level SOP (or POS) implementations • Requires these further timing choices, each with differing timings, to cause multiple glitches

Implementations for Complex Functions and Their Delays • (a) improved: do all signals A B C have the same number of delays to output F9? • (b) improved: how many differing delays do signals X Y Z exhibit in improved circuit F10’? • (b) improved: What is F10? (we are given only F10’) • (b) improved: Is F10’ improved a good design? • (c) prove: all 3 F11 are the same logic function • (c ) how many differing delays do signals A B C D exhibit in the third (lowest) circuit F11?

Hazard Exercise1 • Using And gates, Nand gates, OR gates, and inverters • gate inputs or outputs may also be inverted internally, via inversion bubbles directly at input or output pins • Build circuit for F( A, B, C, D ) = B’D’ + ABC’ + ACD • Step 1: Draw the circuit for the function of 4 variables F( A, B, C, D ) = B’D’ + ABC’ + ACD in SoP form • No need to minimize • We use this same circuit in Step 2

Hazard Exercise1 • Solution to Step 1, others possible: • Circuit for F( A, B, C, D ) = B’D’ + ABC’ + ACD in SoP form

Hazard Exercise1 • Step 2: Using function F( A, B, C, D ) = B’D’ + ABC’ + ACD, draw the Karnaugh map for F() • Identify where static hazards can occur • Add terms to remove these hazards and design a new hazard-free logic function HF()

Hazard Exercise1 • Hazards for F() = B’D’ + ABC’ + ACD can occur at color marked boundaries • To be added: AC’D’ + ABD + AB’C

Hazard Exercise1 • So the hazard free function HF() is: • HF( A, B, C, D ) = • B’D’ + ABC’ + ACD + AC’D’ + ABD + AB’C

Hazard Exercise2 • Explain “static-1 hazard” in a sum-of-products circuit: What causes such a hazard? • Will a correctly designed two-level circuit have static-1 hazards? • How can such hazards be prevented? • What (almost) synonym for hazard is used colloquially, though incorrectly?

Hazard Exercise2 • Explain “static-1 hazard” in a sum-of-products circuit: What causes such a hazard? Different propagation delays through circuit by paths of differing lengths • Will a correctly designed two-level circuit have static-1 hazards? No, because all paths have the same timing • How can static-1 hazards be prevented? By adding further circuitry that solves the timing difference via additional steps in paths; name: consensus path • What (almost) synonym for hazard is used colloquially? Glitch, but keep in mind they are different! Glitch is actual occurrence • But ECE 171 students will avoid such sloppy habits

Hazard Exercise3 • Question1: Explain “dynamic hazard” in a two-level sum-of-products circuit. • Question2: Can they occur in two-level SoP circuit?

Hazard Exercise3 • Question1: Explain “dynamic hazard” in a two-level sum-of-products circuit • Answer1: A dynamic hazard is the repeated change of the output signal caused by a single change of one of the input signals. Happens, when there are multiple paths to the output signal, but each with different delays • Question2: Can they occur in two-level SoP circuit? • Answer2: Cannot occur in two-level SoP, because all delay levels are the same, namely 2!

Hazard Exercise4 • Problem definition: Given function f7() of 4 variables f7( w, x, y, z ) = xy’ + wy + w’x’z, draw its Karnaugh map! • Identify, static-1 Hazards • Compute consensus terms, and add these terms, so a new f7_free( w, x, y, z ) circuit is hazard free!

Hazard Exercise4 Function f7( w, x, y, z ) = xy’ + wy + w’x’z, with Karnaugh map. Now find hazard locations, by analyzing f7():

Hazard Exercise4 • Hazard places are labeled blue (extending to 4 cells in order to minimize terms), yellow (across 4*4 Karnaugh fields), and green • These are the products: w’y’z + wx + x’yz • f7_free() = xy’ + wy + x’w’z + w’y’z + wx + x’yz will be free of hazards; notice, way more complicated!

Hazard Exercise5 • Given the K-Map for function K( a, b, c, d ) below, express K() as a Boolean function in SoP form • Identify where hazards can occur • Devise a hazard-free function K_free( a, b, c, d ) that is functionally equivalent to K()

Hazard Exercise5 • Boolean function: K( a, b, c, d ) = a’ d + a b c

Hazard Exercise5 • Identified hazard locations for K() • Marked in blue:

Hazard Exercise5 • Added term b c d to K() to form K_free() • Consensus term: b c d • K_free() = K() + b c d = a’ d + a b c + b c d