Upgrade intro and report on DESY Upgrade Meeting

Upgrade intro and report on DESY Upgrade Meeting. Norman Gee. 5 May 2010. Background. LHC is designed for running at 10 34 cm -2 s -1 (at present ~10 30 )

Upgrade intro and report on DESY Upgrade Meeting

E N D

Presentation Transcript

Upgrade intro and report on DESY Upgrade Meeting Norman Gee 5 May 2010

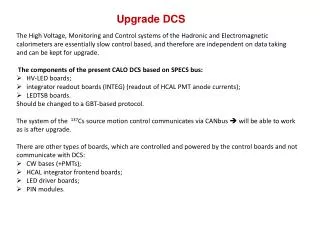

Background LHC is designed for running at 1034cm-2s-1 (at present ~1030) There are plans to increase the luminosity beyond this, to reach an ultimate value of perhaps 5x1034 .This gives an integrated luminosity of 3000 fb-1 by about 2030 , starting to be defined as the end of LHC running There is a long programme of work to bring this to fruition In the LHC and its injectors: LHC collimators, magnet replacements, crab cavities for levelling,… New Linac; significant modifications to PS, Booster, and SPS All this in addition to consolidation work in the present LHC In ATLAS (because detectors can’t handle high or accumulated doses): Additional tracking layer (“IBL”) from ~2015. New inner detector (~2020) Additional muon chambers to improve P resolution, plus shielding Replacement of forward calorimetry and all calorimeter electronics

From Marzio (added red text by NG) Our strategy !? Be ready for sLHC New ID + solve LAr end-caps problems • - Be ready for ultimate Luminosity • - Insert new pixel b-layer • Upgrade various systems for a better and sharper LVL1 trigger Int. Luminosity to 3000 fb -1 Consolidation + new beam pipe Lint ~ 300 fb -1 Lint ~ 50 fb -1 Lp < =2 10 34 Lp ~ 5 10 34 Lp < =10 34 Phase -2 Phase -0 Phase -1 year Lint ~ 1 fb -1 Shutdown requirements : Phase-0 : 12-14 months (defined by the LHC consolidation) Phase-1 : 8-9 months (time necessary to install at least the new pixel b-layer) Phase-2 : 18-20 months to install and debug the new ID detector What are the best dates? When should calo and TDAQ upgrades be done? DESY upgrade week was supposed to identify initial ATLAS preferences 3

Current Level-1 Hardware Trigger Norman Gee- TDAQ/Detectors Intro 4

Possible Phase I Level-1 Trigger Under study, not decided !! Norman Gee- TDAQ/Detectors Intro 5

Possible Phase-II Hardware Trigger Initial ideas, not decided Norman Gee- TDAQ/Detectors Intro 6

Comment on definition of L1 Latency Norman Gee- TDAQ/Detectors Intro 7

DESY - Overview Structure • Monday – pre-meetings • Tuesday - Parallel • Wednesday - Plenary (am), Parallel (pm) • Thursday - Parallel • Friday, Saturday – Plenary Volcano: • 171 names registered. I don’t think I saw more than about half this number at DESY in the meetings I attended • Many people took part by EVO (at least 40 in some sessions). In general worked well (Nigel’s plenary comment: CERN should take note!). For example, radio headsets for speakers, so that sound quality was much higher with microphone in a sensible place rather than buried in clothes Norman Gee- TDAQ/Detectors Intro 8

Notes from Presentations Wednesday Plenary: From initial collision data, particle density per unit eta is slightly higher than highest M/C estimate (Ian Hinchcliffe – see plot below) No mention of future CERN LHC plans in the only talk from LHC LHC prefers to run with 50nS bunches at higher luminosity LAr Parallel R&D is needed to establish if the Rad-hard FADC and high-speed link can be made to work. This is a key issue for upgrade planning There are development plans for a mini-FCAL insert (diamond technology) covering 3.7 < eta <4.7. Potentially interesting for the trigger Norman Gee- TDAQ/Detectors Intro 9

Lar/Tile/L1Calo • LAr/Tile/L1Calo Parallel • Deadtime in the LAr system rises with L1 latency and L1 rate. • With 2.5uS latency, deadtime is 2% at 75kHz and 11% at 100kHz. Could perhaps reduce with CTP trigger rationing? Can improve with fewer readout samples • Detailed estimates of latency for digital system. Currently 2.995uS (nb at LAr), needs careful checking • Fine LAr strip data is essential for effective L1Track matching • GBT: Current Latency measurement is 400 nS for zero-length fibre; but believe that this can be reduced to about 250nS (still 10 clock ticks) in ASIC implementations 23-April-2010 Norman Gee- TDAQ/Detectors Intro 10

Plenary • The hot TDAQ topic has been the hardware trigger • Start to see Monte Carlo simulation results giving justification for trigger upgrades, even at design luminosity • Justification emerging for Phase I Topological trigger, Phase II Track Trigger, MDT-based tracking • Excellent survey of latency from Thilo, we now know that there is 18 BC of spare latency in the current system (or perhaps only 10 in the LAr?) • Probably enough for proposed Phase-I Level-1 upgrade • Need to understand how to optimise this vs CTP leaky bucket algorithm 23-April-2010 Norman Gee- TDAQ/Detectors Intro 11

Plenary - Latency • Beyond Phase I, we need to find a route through difficult (conflicting) boundary conditions in the hardware trigger • Rates from the existing trigger will eventually get too high • BUT can’t (and must not try to) control this by raising thresholds • Need on-calorimeter digitisation to access fine-grain info, + complete new L1 processor to tackle this, and Track Trigger needs fine-grain info • BUT the L0 latency is very close to Muon system limits, perhaps beyond • Rate from L0A trigger (500kHz?) is probably too high for Muon system • BUT track trigger regional readout scheme needs L0A • Latency of MDT trigger is close to (possibly beyond) 3.2 uS limit • BUT very desirable to leave some spare latency in the system 23-April-2010 Norman Gee- TDAQ/Detectors Intro 12

When to Switch from existing ROD spec to a new ROD spec? Not for IBL But if LAr goes digital in 2017? Talks on these issues in TDAQ week (but need preparation before) ROD Development 23-April-2010 Norman Gee- TDAQ/Detectors Intro 13

Specific Issues for L1Calo • We need to collect the best latency estimates we can make for all processing stages • What is the earliest data we could have different phases of L1Calo ready to use • It is VERY IMPORTANT to define this by ATLAS week in Copenhagen • Should we try to build parts of Phase-II early instead of building separate Phase-I?

Comments, questions? 23-April-2010 Norman Gee- TDAQ/Detectors Intro 15