Pemrograman Devais FPGA (Field Programmable Gate Array)

Pemrograman Devais FPGA (Field Programmable Gate Array). Veronica Ernita K. Apa itu FPGA?. FPGA adalah suatu IC program logic dengan arsitektur seperti susunan matrik sel-sel logika yang dibuat saling berhubungan satu sama lain. Memiliki jalur – jalur I/O FPGA yang memadai .

Pemrograman Devais FPGA (Field Programmable Gate Array)

E N D

Presentation Transcript

PemrogramanDevaisFPGA(Field Programmable Gate Array) Veronica Ernita K.

Apaitu FPGA? • FPGA adalahsuatu IC program logic denganarsitektursepertisusunanmatriksel-sellogika yang dibuatsalingberhubungansatusama lain. • Memilikijalur – jalur I/O FPGA yang memadai. • Mempunyaibanyak gate: 5000 s/d juta-an gate • Kecepatan ~100 MHz • MemilikisifatProgrammabletapi, bersifatVolatile.

Programmable • User dapatmemakai IC digital secaraberulang-ulanguntukmenyesuaikan program yang akandidownloadkedalam FPGA. • Volatile • Jikalistrikmatimakasecaraotomatisfungsi FPGA akanhilang, artinya data yang telahdiprosesdandidownloadakanhilangsemuanya.

Mengapamenggunakan FPGA? • Memilikikemampuanuntukmenanganibebankomputasi yang begituberat. • Menghilangkantugas-tugasintensifdariDigital Signal Processing. • Kustomisasiarsitektur agar sesuaidenganalgoritma ideal. • Mengurangibiayasistem. • Efisiensibiaya.

Teknologi FPGA berawaldari? • PROM (Programmable Read Only Memory) • EPROM (Erasable Programmable Read Only Memory) • EEPROM (Electrically Erasable Programmable Read Only Memory) • FLASH • SRAM (Static Random Access Memory)

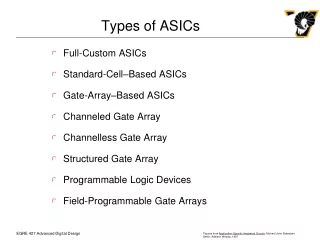

Teknologi yang berhubungandengan FPGA • Transistor, • IC (Integrated Circuit), • SRAM (Static Random Access Memory), • DRAM (Dynamic Random Access Memory), • SPLD (Simple Programmable Logic Devices), • CPLD (Complex Programmable logic Devices), • ASIC

Programmable Logic Device (PLD) • PLD adalah chip general-purpose yang digunakanuntukmengimplementasikanrangkaianlogika(kombinasional). • PLD merupakankomponenelektronik yang dapatdigunakanuntukmembangunrangkaian digital sesuaidengankeinginanperancang. PLD menghubungkanbeberapagerbanglogika yang diaturolehperancanghardware.

Programmable Logic Device (PLD) • Berdasarkanjumlahgerbanglogika yang dimiliki, PLD dapatdibagiatastigatipe,

Simple Programmable LogicDevices (SPLD) • SPLD merupakanalatdengangerbang AND yang dihubungkandengangerbang OR ataugerbang lain yang sejenis. • Gerbang-gerbanginidapatdiatursedemikianrupaolehpemakai. • SPLD dapatdiprogramdenganfusible link, antifuse, EPROM, EEPROM, atau flash.

PLA (Programmable Logic Array) • Merupakanpengembanganpertamadari PLD. • StrukturPLA:

Programmable Array Logic (PAL) • Di PLA, plane AND dan OR keduanyaprogrammable. • Programmable Array Logic (PAL), lebihsederhana: • Plane OR tetap. • PAL lebihmudahuntukdimanufakturdandapatberoperasilebihcepatdaripadaPLA. • Strukturini paling banyakdigunakandiaplikasiyang menggunakanprogrammable device sederhana.

Programmable Array Logic (PAL) • Device PAL mempunyairangkaiantambahandikeluarantiapgerbang OR untukmenyediakanfungsionaltambahan: • Macrocell: gerbang OR dikombinasikan dengan rangkaiantambahan. • PAL = plane AND + macrocell

Complex Programmable LogicDevice (CPLD) • CPLD adalahgabungandaribeberapa SPLD yang dihubungkanolehProgrammable Switching Matrix. • Jadi,CPLD merupakansebuahprogrammable logic device dengankompleksitasantaraProgrammable Array Logic (PAL) dan FPGA.

Karakteristik CPLD • CPLD memilikisifat non-volatile yang diadopsidariPAL. • Memilikibanyakgerbang yang diadopsidariFPGA, meskipungerbang PAL tidaksebanyak FPGA. • Jumlahgerbang yang terdapatpada IC CPLD berkisarantararibuansampairatusanribugerbanglogika.

Logic Block memilikimacrocell yang terdiridarisebuah SPLD dansebuah flip-flop. I/O Block merupakanbagianpada CPLD yang digunakansebagaiinterface data yang akan masuk dan keluar pada CPLD. Programmable Interconnect digunakansebagaipenghubungantarmacrocellatauantara macrocell dengan I/O Block.

Application-Specific Integrated Circuit (ASIC) • ASIC adalah IC yang hanyadigunakanpadakeperluantertentu , kompleksitas IC inicukuptinggijaditidakmuatpada CPLD .

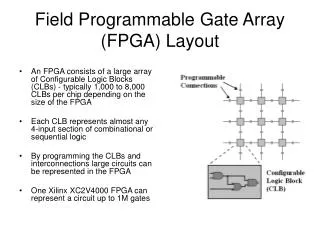

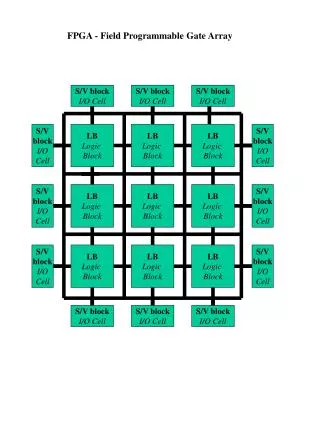

Field Programmable Gate Array (FPGA) • Untukmengimplementasikanrangkaian yang lebihbesarlagi, digunakantipe IC yang dapatmempunyaikapasitaslogika yang lebihbesar: • Field Programmable Gate Array (FPGA) • Tidakberisiblok AND danOR. • Tapi, berisi array bloklogikadanjalurinterkoneksiantarblok. • Jalur interkoneksi disusun sebagai kanal routing secarahorisontaldanvertikal yang berisi programmable switch. • Dapatmengimplementasikanfungsilogikadenganjumlahgerbangekivalenjutaan.

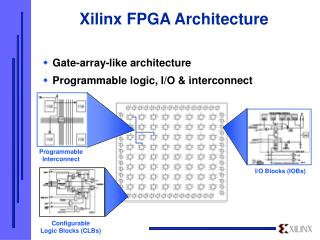

Field Programmable Gate Array (FPGA) Terdiridari: • Configurable Logic Blocks (CLB). • Input/OutputBlocks (IOB). • Programmable Switch Matrix (PSM)

Configurable Logic Blocks (CLB) • CLB merupakanblokuntukmembangunkomponen-komponencombinational/sequential. • UntukdapatmembentukCLB dibutuhkantruth table dalammembangunjalurlogika.

Input/Output Blocks (IOB) • IOB merupakanblok yang digunakanuntukmengirimkansinyalkeluardarichip dansekaligusmembacasinyal yang masukkedalam chip.

Programmable Switch Matrix (PSM) • PSM merupakanpenghubung yang bisadiatursedemikianrupauntukmenghubungkanantar CLB dan CLB denganIOB secarahorizontal maupunsecaravertikal. • Dapatmengeluarkanfan out (kemampuanuntukmengirimkan data kebanyaksumberuntukdijadikan input sekaligus) untukmultiple output. • Jadi, output dari CLB yang satudapatdihubungkankeinput CLB yang lainmelalui multiple PSM.

Design Entry Schematic Entry Text Entry menggunakan VHDL (Verylog Hardware Definition Language)

Functional Simulation • Tujuan: memastikanrancanganrangkaianlogikabekerjasesuaikeinginandenganinput waveforms yang digunakan.

Synthesis • Optimasirangkaianlogikadalampenggunaangerbang. • Menghasilkannetlist yang merupakandaftar connection yang mendeskripsikankomponendanketerhubungankomponentersebut. Implementation • Meliputi: mapping, placing, and routing rancangansehinggadapatdiimplementasikanke IC FPGA sesuaiarsitekturdankonfigurasi pin IC FPGA tersebut.

Timing Simulation • Verifikasirangkaianapakahsudahbekerjapadafrekuensi yang diinginkandantidakadapropagation delay.

Device Programming • Membuatbitstream yang merepresentasikanrancanganakhirdanakandikirimke target device.