Efficient Verification Techniques for Effective Reuse in Chip Design Projects

Discover strategies for maximizing reuse from project to project in chip design, covering BFMs, protocols, assertions, tests, drivers, and more.

Efficient Verification Techniques for Effective Reuse in Chip Design Projects

E N D

Presentation Transcript

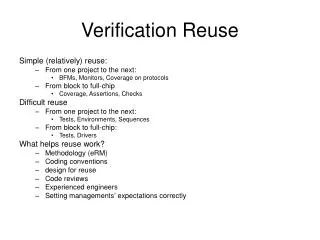

Verification Reuse Simple (relatively) reuse: • From one project to the next: • BFMs, Monitors, Coverage on protocols • From block to full-chip • Coverage, Assertions, Checks Difficult reuse • From one project to the next: • Tests, Environments, Sequences • From block to full-chip: • Tests, Drivers What helps reuse work? • Methodology (eRM) • Coding conventions • design for reuse • Code reviews • Experienced engineers • Setting managements’ expectations correctly

Classic eRM Agent Passive Active Config Seq driver Signal map BFM Monitor DUT

Block level testing Golden Model Scoreboard Monitor Monitor DUT BFM Generator BFM

Full Chip level testing Golden Model Scoreboard Golden Model Golden Model Scoreboard Scoreboard Monitor Monitor Monitor Monitor DUT DUT Generator BFM BFM A B