Asynchronous comparator design

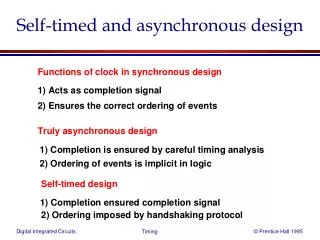

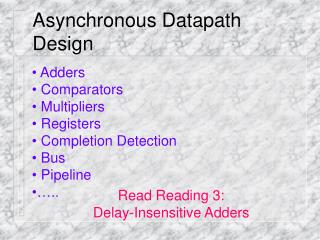

Asynchronous comparator design. Motivation Background: Sync and Async comparators Delay-insensitive carry-lookahead comparators Complexity Analysis Conclusions. Motivation. Comparison is one of the most important operations in digital systems.

Asynchronous comparator design

E N D

Presentation Transcript

Asynchronous comparator design • Motivation • Background: Sync and Async comparators • Delay-insensitive carry-lookahead • comparators • Complexity Analysis • Conclusions

Motivation • Comparison is one of the most important • operations in digital systems. • Comparators are used in ALUs, cache memory, • MMU and data hazard detection. • Integer comparison: use an integer adder. • Problem: addition time > comparison time. • High speed comparison is needed.

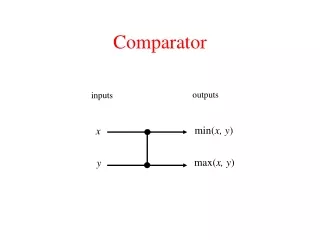

Background: Binary Comparison • Worst case: A=B • A: 01101110 • B: 01101110 • Best case: A>B • A: 01101110 • B: 10101110 • Comparators can perform average case behavior

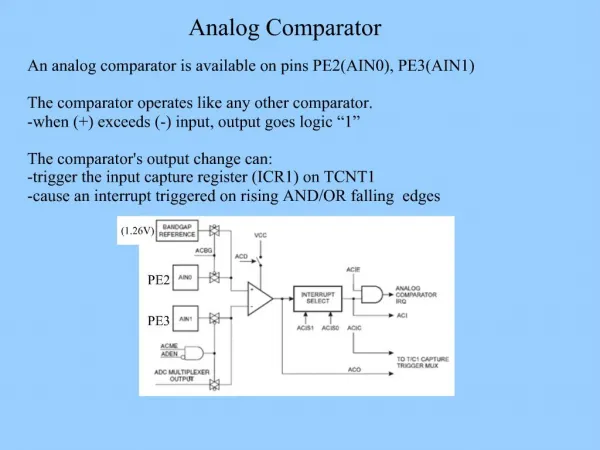

Background • Ripple-Carry Comparator(Sync): • Flow table specification:

Background • Delay-Insensitive Ripple-Carry Comparator: • Flow table:

Background • Ripple-Carry Comparator: • Logic complexity: O(n) • Time complexity: O(n) • Delay-Insensitive Ripple-Carry Comparator: • Logic complexity: O(n) • Time complexity: O(1)

Carry-Lookahead Comparators • RCC requires n stage-propagation delays. • Use carry-lookahead comparators(CLC). • CLCs: • Logic complexity: O(n) • Time complexity: O(log n)

8-bit carry-lookahead comparator

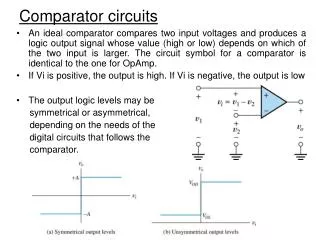

DI Carry-Lookahead Comparator • Delay-Insensitive Carry-Lookahead Comparators • may be implemented by using delay-insensitive • code. • 1. dual-rail signaling: input bits • 2. one-hot code: internal signals, s, g, e (S, G, E). • S: smaller (A<B) • G: greater (A>B) • E: equal (A=B)

CMOS Implementation • DI P-module:

CMOS Implementation • DI I-module:

CMOS Implementation • DI SI-module: 3 2-input AND gates.

CMOS Implementation • Speed-up circuits for S and G signals: • Dynamic OR • gates.

CMOS Implementation • Speed-up circuits for E signals: • Dynamic OR gate:

SPICE Simulation: • SPICE Simulation contains two parts: • Random number inputs: • 10000 random generated input pairs • Statistical data: • running examples on a 32-bit ARM • emulator

SPICE Simulation: • Random number inputs: • 10000 random generated input pairs • a. RCC: 32.4ns • b. CLC: 6.2ns

SPICE Simulation: • Confidence Limits:

SPICE Simulation: • Confidence Limits:

SPICE Simulation: • Distribution of typical-case comparisons:

SPICE Simulation: • SPICE simulation • results: • dynamic traces

Conclusions • A new pratical design of DI comparator. • Theoretically, • Logic Complexity:((n)). • Time Complexity:((1)). • Reality: • more than 2 times faster than its sync • counterpart with 80% usable clock. • Suitable for VLSI implementation.