Formal Composition for TTA – SRI International

10 likes | 141 Vues

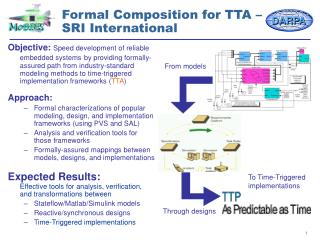

This project aims to accelerate the development of reliable embedded systems by establishing a formal connection between industry-standard modeling techniques and time-triggered implementation frameworks. By utilizing formal characterizations of widely-used modeling, design, and implementation frameworks through tools like PVS and SAL, we seek to develop robust analysis and verification tools. The objective includes creating formally-assured mappings between models, designs, and implementations, particularly for Stateflow, Matlab, and Simulink models, resulting in effective transformations to time-triggered implementations.

Formal Composition for TTA – SRI International

E N D

Presentation Transcript

Objective: Speed development of reliable embedded systemsby providing formally-assured path from industry-standard modeling methods to time-triggered implementation frameworks (TTA) Approach: Formal characterizations of popular modeling, design, and implementation frameworks (using PVS and SAL) Analysis and verification tools for those frameworks Formally-assured mappings between models, designs, and implementations Expected Results:Effective tools for analysis, verification, and transformations between Stateflow/Matlab/Simulink models Reactive/synchronous designs Time-Triggered implementations Formal Composition for TTA –SRI International From models To Time-Triggered implementations Through designs