Enhancing Clock Network Tolerance through Cross-Link Insertion Techniques

270 likes | 392 Vues

This paper presents innovative methodologies for clock network synthesis (CNS) to improve tolerance against variations in VLSI technology. Introducing cross-link insertion among internal nodes significantly reduces clock skew while maintaining power efficiency. Experimental results demonstrate an average capacitance reduction of 32% compared to top competitors in the ISPD-2010 design contest. Our approach effectively addresses the challenges posed by power supply and wire width variations, paving the way for robust clock distribution networks.

Enhancing Clock Network Tolerance through Cross-Link Insertion Techniques

E N D

Presentation Transcript

Cross Link Insertion for ImprovingTolerance to Variations in ClockNetwork Synthesis Tarun Mittal and Cheng-KokKoh School of Electrical and Computer Engineering Purdue University

Outline • Introduction • Motivation • Clock network synthesis • Experimental results • Conclusions

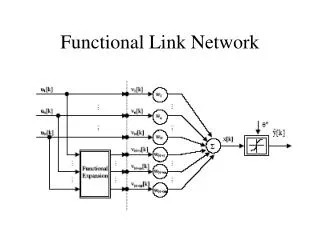

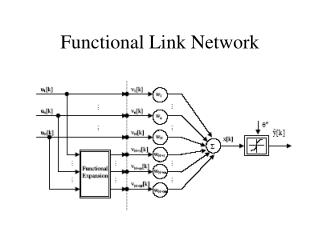

Introduction • Clock network synthesis (CNS) • Clock skew • Buffer insertion • Power reduction • With the scaling of the VLSI technology • Power supply and wire width variationshave a significant impact on the performance of the clock distribution networks. • Tree structure • Non tree structure • Reducing skew variability • Mesh • Cross link

Introduction • Mesh • Effective in reducing skew variability • Larger area • Power overheads • Cross link • A cost effective alternative for reducing skew variability

Motivation • Qualitative analysis R: resistance C: capacitance Rloop: total resistance along p->u->v->p

Qualitative analysis Link is inserted between two sinks u and v Link is inserted between two higher level internal nodes u and v

Scenario 1 • Method 1 • m and n have different path lengths to u • Skew variability is different • Method 2 • m and n have same path lengths to u • Skew variability is same

Scenario 2 • Method 1 • Different delays within a subtree • Non uniform correlation betweenthe delays of m and n • Method 2 • Same delays within a subtree • Uniform correlation betweenthe delays of m and n

Scenario 3 • Since there is no overlap between the source-to-n path and Tp, there is no predictable correlation between the delays of nodes m and n.

Experiment 1 • Effect of αon the skew variations • because of α2< α1( β2<β1 )

Experiment 1 • Effect of αon the skew variations • because of α2< α1( β2<β1)

Experiment 2 • Effect of the link on the delays of the sinks within a subtree

Experiment 2 • Effect of the link on the delays of the sinks within a subtree

Experiment 3 • Effect of change in αon the skew variability • Adding detour lengths to cross links in experiment 1 Worst case skew (WCS)

Experiment 4 • Compare cross link inserted above the buffers versus cross link inserted below the buffers

Clock network synthesis • Problem Formulation • ISPD 2010 High performance clock network synthesis • Based on method 2 for cross link insertion • Consists of 3 main steps • Merging • Buffer insertion • Link insertion

Problem formulation • Given: Sinks, Blockages and clock source location • Objective: Generate a clock network T that connects clock source to the sinks. • Constraints: • All sink pairs with distance between them less than user specified distance are called local sink pairs. • All local sink pairs should satisfy Local clock skew constraint (LCS). • Slew at any point should be less than predefined limit S. • Buffers should not be placed in the blockages

Deferred merge embedding (DME) • Top-down phase is identical to DME

Merging • Bottom up phase • Nearest Neighbor Graph (NNG)

Conclusion • A new link insertion methodology, where links are inserted between pairs of internal nodes in a clock tree. • Improves the correlation of sink delays for sinks that have similar path lengths to an inserted cross link. • Average 32% lower capacitance than the least capacitance obtained by the top three teams in the ISPD-2010 design contest