Registers

Registers. VHDL Tutorial R. E. Haskell and D. M. Hanna T2: Sequential Logic Circuits. An 8-bit register. d(7 downto 0). clr. reg. clk. load. q(7 downto 0). Register entity. Register architecture. architecture reg_arch of reg is begin process (clk, clr) begin

Registers

E N D

Presentation Transcript

Registers VHDL Tutorial R. E. Haskell and D. M. Hanna T2: Sequential Logic Circuits

An 8-bit register d(7 downto 0) clr reg clk load q(7 downto 0)

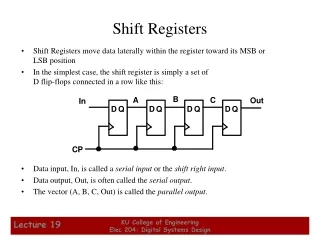

Register architecture architecture reg_arch of reg is begin process(clk, clr) begin if clr = '1' then q(i) <= "00000000"; elsif (clk'event and clk = '1') then if load = '1' then q <= d; end if; end if; end process; end reg_arch; Infers a flip-flop for all outputs (q)

debounce entity entity debounce is port ( inp, clk, clr: in std_logic; outp: out std_logic ); end debounce; clk clr inp debounce outp

outp inp delay1 delay2 delay3 clk debounce

outp inp delay1 delay2 delay3 clk

debounce architecture architecture rtl of debounce is signal delay1, delay2, delay3: std_logic; begin process(clk, clr) begin if clr = '1' then delay1 <= '0'; delay2 <= '0'; delay3 <= '0'; elsif clk'event and clk='1' then delay1 <= inp; delay2 <= delay1; delay3 <= delay2; end if; end process; outp <= delay1 and delay2 and (not delay3); end rtl;

Lab Exercise T2 Debounce Simulation using Aldec Active-HDL 4.1