Automatic Test Program Generation for Muti -core Processors

Automatic Test Program Generation for Muti -core Processors. Version 1.1. Speaker: Hung-Yi Chen Advisor: Chun-Yao Wang 7/8/2008. Outline. Introduction Assignment Decision Diagram Tsing-Hua Logic Format Test Program Generation Future work. Introduction (1/2).

Automatic Test Program Generation for Muti -core Processors

E N D

Presentation Transcript

Automatic Test Program Generation for Muti-core Processors Version 1.1 Speaker: Hung-Yi Chen Advisor: Chun-Yao Wang 7/8/2008

Outline • Introduction • Assignment Decision Diagram • Tsing-Hua Logic Format • Test Program Generation • Future work

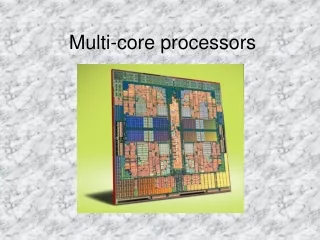

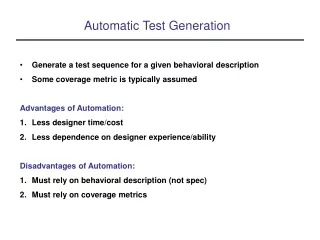

Introduction (1/2) Functional verification plays an important role in checking the functionality of the design during the design flow. Verification of processor architecture designs consumes more than 70% of the total concept-to-silicon transformation time.

Introduction (2/2) The current practice is to generate millions of random test instructions. But the random test generation does not guarantee the coverage of all the functionalities, especially in the case of complex designs.

Assignment Decision Diagram (1/4) The ADD is a complete, efficient, and “partially” unique representation.

Assignment Decision Diagram (2/4) ADD is “partially” unique because it can uniquely represent a set of description that are written with different grouping and ordering of conditional and assignment statements. Grouping Ordering

Assignment Decision Diagram (4/4) An example : Translation Scheduling

Tsing-Hua Logic Format (1/7) THLF is a text-based representation to depict each assignment target’s behaviors. [Active Signal] Assignment Condition : Assignment Target = Value ; always @(posedge CLK) begin D = 0; while (D<E) begin A <= D + A; D <= D + 1; end A = 0; end [CLK] Posedge CLK : ST = st1; [ST, D, E] ST = st1 & (D<E) : ST = st2; [ST, D, E] ST = st1 & ~(D<E) : ST = st3; [ST, D, E] ST = st2 & ~(D<E) : ST = st3; [ST] ST = st1 : D = 0; [ST] ST = st2 : A <= D + A; [ST] ST = st2 : D <= D + 1; [ST] ST = st3 : A = 0;

Tsing-Hua Logic Format (2/7) THLF deals with Non-Blocking and Blocking assignments as two different groups. always @(posedge CLK) begin A = B + 1; C <= B + 2; C = B + 1; A <= B + 2; end [CLK] Posedge CLK : ST = st1; [ST] ST = st1 : A = B + 1; C = B + 1; [ST] ST = st1 : C <= B + 2; [ST] ST = st1 : A <= B + 2; always@(posedge CLK) ST = st1; always@(ST) if (ST == st1) A=B+1 … always@(ST) if (ST == st1) C<=B+2; always@(ST) if (ST == st1) A<=B+2;

Tsing-Hua Logic Format (3/7) THLF is a machine description that is used to describe the FF/latch/wire’s behaviors under each conditions (including more asynchronous behaviors). Retention Register Vdd Qret [CLK] Negedge CLK : Q = D; [RST] Posedge RST : Q = 0; [Save ] Save = 0 : Qret = Q; [Restore] Restore=0 : Q = Qret; … Restore# Save# Q FF D CLK# RST

Tsing-Hua Logic Format (4/7) S0 State 0 : @ PosEdge CLK always @(posedge CLK) begin D = 0; while (D<E) begin A <= D + A; D <= D + 1; end A = 0; end PosEdge CLK State 1 : S1 D >= E D = 0; While (D<E) D < E State 2 : A <= D+A; D <= D+1; S2 D >= E State 3 : A = 0; S3 State Transition Graph (STG)

Tsing-Hua Logic Format (5/7) We can use “Program Slicing” to build the data dependence graph. 0 S3 Relevant Set 1: D = 0; A 2: A <= D+A; A , D 3: D <= D+1; A 4: A = 0; A S2 D A S1 0 Slice <A,4> = D = 0; A A <= D+A; A , D A = 0; A Data Dependence Graph (DDG)

Tsing-Hua Logic Format (6/7) But, the “Program Slicing” is a time-consuming process on slicing the sequential circuits. 0: Always@(posedge CLK) begin 1: d <= e; 2: c <= d; 3: b <= c; 4: a <= b; 5: end Slice : d <= e; c <= d; b <= c; a <= b; 0: Always@(posedge CLK) begin 1: a <= b; 2: b <= c; 3: c <= d; 4 : d <= e; 5: end Slice : a <= b;

Tsing-Hua Logic Format (7/7) The relationships between Verilog, ADD and THLF are similar to that between C, assembly and machine code. Verilog/VHDL … C / C++ … ADD Assembly Language THLF Machine Code

Test Program Generation (1/4) It’s a two-phases “Test Program Generation (TBD)” algorithm. Definition 1: 1. Phase 0 is “Computation Phase”. 2. Phase 1 is “Store Phase”. Comb FF Comb FF Computation Phase Store Phase Time Frame X

Test Program Generation (2/4) Definition 2: “TestProgramVector” = { [ Variable_Name = Values; TimeFrame# ] cond […] } For example : 1. { [EXEReg_OP = 00,01; -1] } 2. { [EXEReg_OP = ?; 0] = [InstReg[7:6] = ?; -1] } 3. { [EXEReg_OP = 00~11; 0] }

Test Program Generation (3/4) An example : always@(posedge CLK) begin if (EXE == 00) DEBUG_EN <= 1; WB <= MEM; MEM <= EXE; EXE <= DE; DE <= InstrReg; end S0 InstReg PosEdge CLK 1 S3 S1 DE EXE != 00 S2 DEB EXE == 00 S3 S2 EXE S3 MEM S3 (DDG) (STG) S3 WB

Test Program Generation (4/4) {[ Inst=00; -2]} Then, we want to activate the S2 state. (DEBUG_EN <= 1) S0 InstReg PosEdge CLK 1 S3 {[ DE=00; -1]} S1 F DE 1 S2 No DEBUG_EN {[ EXE=00; 0 ]} T DEB EXE == 00 {[ EXE=00; 0]} S3 EXE == 0 S2 EXE {[ ? ; 0 ]} S3 {[DE=0;-1]} DE =>EXE {[EXE=0;0]} MEM S3 {[ Inst=00; -2]} {[ 1 ; -1 ]}1 =>DEBUG_EN{[ ? ; 0 ]} S3 CLK WB

Future Work 1. Figure out an appropriate method to find out FSM paths that are used to generate test programs. 2. Study more papers on processor verification field.