Automatic Test Program Generation for Muti -core Processors

Automatic Test Program Generation for Muti -core Processors. Version 1.0. Speaker: Hung-Yi Chen Advisor: Chun-Yao Wang 6/3/2008. Outline. Introduction Previous Works Assumptions of these pervious works An overview of our approach Assignment Decision Diagram

Automatic Test Program Generation for Muti -core Processors

E N D

Presentation Transcript

Automatic Test Program Generation for Muti-core Processors Version 1.0 Speaker: Hung-Yi Chen Advisor: Chun-Yao Wang 6/3/2008

Outline • Introduction • Previous Works • Assumptions of these pervious works • An overview of our approach • Assignment Decision Diagram • Tsing Hua Logic Format (TBD) • Test Program Generation • Future works

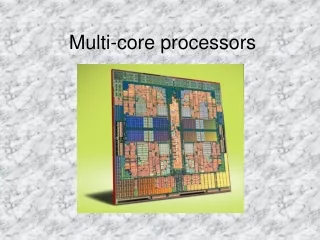

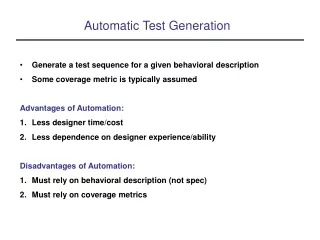

Introduction The continuous advances in the design field are creating a signification challenge to verification. 1. Verification process is a time-consuming task during the whole design flow. 2. The current practice is to generate millions of random test instructions. 3. The random test generation does not guarantee the coverage of all the functionalities, especially in the case of complex designs.

Previous works 1. “Automatic Test Pattern Generation for Functional RTL Circuits Using Assignment Decision Diagrams” In Proceedings of Design Automation Conference 2000. Indradeep Ghosh and Masahiro Fujita. 2. “Automatic Design Validation Framework for HDL Description via RTL ATPG” In Proceedings of the Asian Test Symposium 2003. Indradeep Ghosh et al. 3. “A Framework for Automatic Assembly Program Generator (A2PG) for Verification and Testing of Processor Cores” In Proceedings of the Asian Test Symposium 2005. Kailasnath Maneparambil (Intel) et al.

Previous works 4. “Automatic Constraint Based Test Generation for Behavioral HDL Models” ??? 2007. Siva Kumar (Intel) et al.

Previous works The ADD-based algorithms make the following assumptions: • - The RTL design is in VHDL/Verilog and has a single clock line. • - The circuit does not have any complicated asynchronous behavior other than set/reset of flip-flops. • - The functionality of black boxes or intellectual properties (IPs) are stated such that each input of the block can be propagated to an output or a combination of outputs of the block in a fixed number of cycles and each output of the block can be justified from an input or combination of inputs of that block in a fixed number of cycles. … • - Each finite state machine (FSM) description in the RTL circuit has a reset state or a single input line that takes the FSM to a fixed state when it is set or reset.

An overview of our approach Verilog VHDL SystemC ADD THLF (TBD) Test Program Generator

Assignment Decision Diagram The ADD is a complete, efficient, and “partially” unique representation.

Assignment Decision Diagram ADD is “partially” unique because it can uniquely represent a set of description that are written with different grouping and ordering of conditional and assignment statement . Grouping Ordering

Assignment Decision Diagram ADD provided a text-based description/equation. Assignment Index Assignment Action Assignment Condition Assignment Value Assignment Target & Temporary signal

Assignment Decision Diagram An Example : Translation Scheduling

TsingHua Logic Format THLF is a text-based representation to depict each assignment target’s behaviors. [Trigger Signal] Assignment Condition : Assignment Target = Value ; always @(posedge CLK) begin D = 0; (st1) while (D<E) begin (st2) A = D + A; (st2) D = D + 1; (st2) end A = 0; (st3) end [Posedge CLK] 1 : ST = st1; [1] ST = st1 : D = 0; [1] ST = st1 & (D<E) : ST = st2; [1] ST = st1 & ~(D<E) : ST = st3; [1] ST = st2 & ~(D<E) : ST = st3; [1] ST = st2 : A = D + A; [1] ST = st2 : D = D + 1; [1] ST = st3 : A = 0;

TsingHua Logic Format THLF is a machine description, that is used to descript the FF/latch/wire’s behaviors under each conditions (including more asynchronous behavior). Retention Register Vdd Qret [Negedge CLK] 1 : Q = D; [Posedge RST] 1 : Q = 0; [Save == 0] 1 : Qret = Q; [Restore == 0] 1 : Q = Qret; … Restore# Save# Q FF D CLK# RST

TsingHua Logic Format THLF also supports muti-clock design. Comb Comb Comb FF FF FF Clock Domain 1 Clock Domain 2 Clock Domain 3 … … [Posedge CLK1] 1:Q = D; … … [Posedge CLK2] 1:Q = D; … … [Posedge CLK3] 1:Q = D;

TsingHua Logic Format The relationships between Verilog, ADD and THLF is similar to that between C, Assembly and machine code. Verilog/VHDL … C / C++ … ADD Assembly Language THLF Machine Code

Test Program Generation Q1 : How to find out a path can visit as many state as possible ? High code coverage ? D<E Otherwise D<E st0 st2 st1 Posedge CLK ~(D<E) st3 ~(D<E)

Test Program Generation Q2 : How to improve efficiency on the path we found in Q1 ? reduce the loop count ? D<E Otherwise D<E st0 st2 st1 Posedge CLK ~(D<E) st3 ~(D<E)

Future Works 1. Figure out an appropriate method to find out FSM paths that are used to generate test programs. 2. Study more papers on processor verification field.