Reducing Structural Bias in Technology Mapping - A Comprehensive Study

340 likes | 364 Vues

This research explores methods to minimize structural bias in technology mapping, focusing on supergates, lossless synthesis, and Boolean mapping. It discusses the challenges of finding optimal matches and proposes innovative solutions. The study highlights the importance of efficient choice operators and quick mapping techniques for improved results. Various approaches like cut-based Boolean mapping and dynamic programming on a DAG are explained in detail to achieve delay optimality. Overall, the paper offers valuable insights into enhancing technology mapping processes and reducing biases effectively.

Reducing Structural Bias in Technology Mapping - A Comprehensive Study

E N D

Presentation Transcript

Reducing Structural Bias in Technology Mapping Satrajit Chatterjee, Alan Mishchenko and Robert Brayton U. C. Berkeley Xinning Wang and Timothy Kam Intel Corp. ICCAD / 8 Nov 2005

Outline • Structural Bias • Supergates • Lossless Synthesis • Boolean Mapping • Experimental Comparison

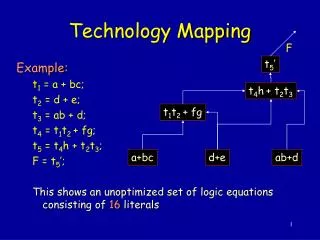

0 1 Technology Mapping Input: A set of gates and a Boolean network Output: A netlist of gates imple- menting the Boolean network f f Technology Mapping a c d b a c d b The subject graph The mapped netlist The library

Structural Bias The mapped netlist very closely resembles the subject graph f f p p a c d b a c d b Every input of every gate in the mapped netlist must be present in the subject graph .. .. otherwise technology mapping will not find the match

The Problem of Structural Bias A better match may not be found f This match is not found f f p 0 1 p q a c d b a c d b a c d b Since the point q is not present in the subject graph, the match on the extreme right will not be found

Outline • Structural Bias • Supergates • Lossless Synthesis • Boolean Mapping • Experimental Comparison

0 1 0 1 Supergates Idea: Combine multiple library gates into a single gate for mapping Supergate Generation Examples of some supergates generated from the library The library

Supergates Help Since the whole supergate is matched at a time, the presence of intermediate points is not required in the subject graph f f 0 1 r q r a c d b a c d b Observe that the point q is not required in the subject graph since it is now an internal point of the supergate, so the match is found

Generating Supergates • Supergates are pre-computed from the library • Currently generating exhaustively by combining all possible gates within resource limits • This simple method is quite effective • Details in the paper • Could be more clever: Look at the circuits for most commonly occurring functions • Generate supergates for those using expensive constructive techniques • A mapper that improves over time!

f 0 1 p q a c d b Using Supergates Need Boolean Matching • Interesting supergates are unlikely to be simple tree structures • Need a very fast matching algorithm since having supergates greatly increases the library size

Outline • Structural Bias • Supergates • Lossless Synthesis • Boolean Mapping • Experimental Comparison

Traditional Synthesis Only the network at the end of technology independent synthesis is used for mapping Boolean Network Technology- independent synthesis sweep eliminate resub simplify No guarantee of optimality since each synthesis step is heuristic. But structural bias means the mapped netlist depends heavily on the final network. fx resub sweep eliminate sweep full simplify Technology Mapping Mapped Netlist

Lossless Synthesis Idea: Merge intermediate networks into a single network with choices which is used for mapping Technology- independent synthesis Boolean Network sweep eliminate resub simplify Choice operator Technology mapping is not any harder with choices (Lehman/Watanabe ‘95) fx resub sweep eliminate sweep full simplify Technology Mapping Mapped Netlist

Lossless Synthesis Can combine the results of different technology independent optimization scripts Script optimizes area Boolean Network sweep Script optimizes delay eliminate resub simplify speed up reduce depth fx resub sweep eliminate sweep full simplify Technology Mapping Mapped Netlist

Mapping with Choices Boolean Network sweep eliminate resub simplify Question 1: How to implement an efficient choice operator? fx resub sweep Question 2: How to map quickly with choices? eliminate sweep full simplify Technology Mapping Mapped Netlist

y x a c d b Detecting Choices Task: Given two Boolean networks, we need to create a network with choices Network 1 x = (a + b).c y = b.c.d Network 2 x = a.c + b.c y = b.c.d Step 1: Make And-Inverter decomposition of networks y x a c d b

y x a c d b Detecting Choices Step 2: Use combinational equivalence to detect functionally equivalent nodes up to complementation (Kuehlmann ’04, …) • Random simulation to detect possibly equivalent nodes • SAT-based decision procedure to prove equivalence Network 1 x = (a + b).c y = b.c.d Network 2 x = a.c + b.c y = b.c.d x y a c d b

y x a c d b x y a c d b Detecting Choices Step 3: Merge equivalent nodes with choice edges x y a c d b x now represents a class of nodes that are functionally equivalent up to complementation

Outline • Structural Bias • Supergates • Lossless Synthesis • Boolean Mapping • Experimental Comparison

Overview of Mapping Cut-based Boolean mapping using dynamic programming on a DAG for delay optimality Input: And-Inverter Graph with choices • Compute 5-feasible cuts • Compute truth-tables of cuts • Boolean Matching • Compute best arrival time at each node • Chose the best cover Output: Mapped Netlist Only Step 1 needs to be modified to handle choices

k-feasible Cuts r (Rough definitions) A cut of a node n is a set of nodes in transitive fan-in such that assigning values to those nodes fixes the value of n. A k-feasible cut means the size of the cut must be k or less. p q a b c The set {p, b, c} is a 3-feasible cut of node r. (It is also a 5-feasible cut.) k-feasible cuts are important in Boolean matching, because the logic between a node and the nodes in its cut can be replaced by a suitable gate from the library.

k-feasible Cut Computation The set of cuts of a node is a ‘cross product’ of the sets of cuts of its children { {r},{p, q}, {p, b, c},{a, b, q}, {a, b, c} } r { {p},{a, b} } { {q},{b, c} } Computation is done bottom-up p q { {b} } { {c} } { {a} } a c b Any cut that is of size greater than k is discarded (Pan ’98, Cong ’99)

Cut Computation with Choices Cuts are now computed for equivalence classes of nodes { {x2}, {q, c}, {a, b, c} } { {x1}, {p, r}, {p, b, c}, {a, c, r}, {a, b, c} } x y x1 x2 r p q a c d b Cuts ( x ) = Cuts ( x1) Cuts( x2 ) = { {x1}, {p, r}, {p, b, c}, {a, c, r}, {a, b, c}, {x2}, {q, c} }

Mapping Algorithm Subsequent steps do not require modification to handle choices Input: And-Inverter Graph with choices • Compute 5-feasible cuts • Compute truth-tables of cuts • Boolean Matching • Compute best arrival time at each node • Chose the best cover Output: Mapped Netlist

Outline • Structural Bias • Supergates • Lossless Synthesis • Boolean Mapping • Experimental Comparison

Experimental Comparison Comparison of various techniques to reduce structural bias (Current version / newer than paper) Baseline is fast: 10K gates in 3 sec. Choice detection run-time is 3x baseline. Comparison with algebraic choices (a la Lehman-Watanabe) Delay improvement over the mode

Experimental Comparison Comparison with other mappers on industrial examples

Conclusions • Supergates and Lossless synthesis • Reduce structural bias, improve QoR significantly • Compose and scale • Supergates • Simple generation is effective • Fit neatly with (simplified) Boolean Matching algorithm that we use (but didn’t talk about) • Pre-computation to eliminate NPN-canonicization and pin correspondence • Explore Boolean decompositions • Lossless synthesis • Use structural equivalence checking to find choices • Natural extension of Boolean matching • A different perspective on synthesis • Think of different ways to add choices and let the mapper decide

Current Research • Integration with physical synthesis • Using table-lookup load-based delay models • Sizing • Placement-awareness

Questions Mapper along with Choice Detection implemented in MVSIS. Available for download from the MVSIS website. Google: “berkeley technology mapping”

Comparison with Lehman-Watanabe • Extension of Boolean matching to handle choices • Handles complex gates • Fast • Use of structural equivalence checking to detect choices • Works on large circuits • Use of intermediate networks during a flow • Quantified gains from each technique • Supergates explore Boolean decompositions as opposed to algebraic ones • Simpler implementation

Experimental Comparison (Old) Comparison of various techniques to reduce structural bias Baseline is fast: 10K gates in 3 sec. C, L times include choice detection.

Experimental Comparison Comparison with DAG Map