Using the SDRAM Controller on Field Programmable Port Extender (FPX)

120 likes | 139 Vues

Learn about the advanced features of the SDRAM controller module in Field Programmable Port Extender (FPX) for improved memory management and data throughput.

Using the SDRAM Controller on Field Programmable Port Extender (FPX)

E N D

Presentation Transcript

Using the SDRAM Controller on Field Programmable Port Extender (FPX) Sarang Dharmapurikar Washington University, Applied Research Lab August 15, 2001 Supported by: NSF ANI-0096052 and Xilinx Inc. http://www.arl.wustl.edu/arl/projects/fpx

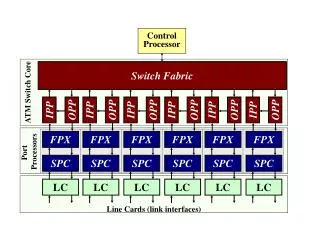

SDRAM Controller Overview SDRAM Controller Module 0 SDRAM Module 1 Module 2

SDRAM Controller Features • Arbitrates between multiple memory requests • Maintains sequential consistency for each module • Maximizes the SDRAM throughput by - Re-ordering memory requests based on addresses and operation type - Favoring the locality in memory access • Increases throughput for higher locality

SDRAM controller performance 1 FPX SDRAM controller trivial controller enhanced trivial controller 0.9 Per-bank row register conventional controller single bank row register conventional controller 0.8 SDRAM data bus utilization 0.7 0.6 0.5 0.4 0 0.2 0.4 0.6 0.8 1 Locality Effect of locality on the SDRAM data bus utilization

SDRAM Controller Usage Request Request(n) Grant1 Grant1(n) Grant2 Grant2(n) InfoBus InfoBus To SDRAM DataBus DataBus SDRAM Controller Module n

Protocol Data Transaction Make Request Wait Grant1 yes No Grant1? Grant2? No yes Send Address Send Burst Length Send Op Type Wait Grant2

Example : Leaky Bucket • What does it do? - Buffers the incoming cells in a FIFO - Generates tokens at a regular interval - Gives out a cell from the FIFO when the number of tokens > 0 - Destroys a token when a cell is given out bursty data leaking data

Example : Leaky Bucket Implementation Read Request Soc_out Write Request Soc_in Read Grant Tca_in Write Grant Tca_out Read Data Data_in Write Data Data_out 64 64 32 32 SDRAM SDRAM Controller Send Cell Pull Cell Get Cell Push Cell Cell FIFO

Example : Leaky Bucket Testbench SDRAM SDRAM Controller Send Cell Pull Cell Get Cell Push Cell Cell FIFO 64 32 32 64 CELLOUT.DAT TESTCELL.DAT Fake_nid_out Fake_nid_in

Exercise • Take a walk through Leaky Bucket • Wire up Cell FIFO in Leaky Bucket • Wire up Leaky Bucket, SDRAM controller in test-bench • Change the parameters - c_MaxTokenCount - c_PaceInterval • Try different traffic patterns and verify the Leaky Bucket functionality