DDR SDRAM Controller Core

DDR SDRAM Controller Core . DSD Opencores Project 資訊三 B92902069 楊博翔. What is “DDR” ?. DDR SDRAM, or simply DDR, is the acronym for Double Data-Rate Synchronous DRAM (SDRAM). SDRAM used only the rising edge of the clock cycle to transfer data.

DDR SDRAM Controller Core

E N D

Presentation Transcript

DDR SDRAM Controller Core DSDOpencores Project 資訊三 B92902069楊博翔

What is “DDR” ? • DDR SDRAM, or simply DDR, is the acronym for Double Data-Rate Synchronous DRAM (SDRAM). • SDRAM used only the rising edge of the clock cycle to transfer data. • DDR SDRAM transfers data on both the rising and falling edge of the clock.

For example… • 100MHz的SDRAM利用DDR技術處理後 → 200MHz的DDR SDRAM。(Because clock is shrink to half)

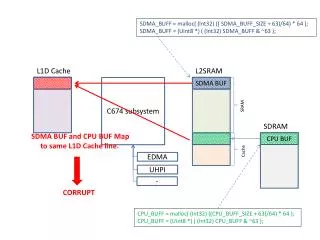

Primary blocks 1. Control & Timing Block 2. Initialization Control 3. Address Generation 4. Bank Management 5. Refresh Control 6. DDR Data Control

Instruction Timing • Initialization 1.No operation command for 200μs 2.Precharge-all command 3.Load some Register command 4.Precharge-all command 5.2 auto refresh commands 6.Load some Register command 7.Read/write requests held off for 200 clocks

Auto-Refresh • SDRAM devices require periodic auto-refresh commands to maintain data integrity. • Occurs when one or more banks have been left open as a result of a read without precharge or write without precharge. • All open banks are closed using the precharge-all command.

Bank Management • For each bank, the controller records the last opened row, and whether the bank has been closed. • If the bank was not closed → Use precharge command & use active command to re-open the bank. • If the bank was closed → Controller uses active command to open the bank to the requested row.

SDRAM Writes • The user writes to the local bus interface by asserting the w_req signal and driving the starting address and burst size on raddr and b_size. • auto_pch is asserted with w_req to cause the write to be issued as a write with auto-precharge.

SDRAM Reads • The user reads from the local bus interface by asserting the r_req signal and driving the starting address and burst size on raddr and b_size. • auto_pch is asserted with r_req to cause the read to be issued as a read with auto-precharge.

Auto-Precharge • If the auto-precharge option is used, the SDRAM device will automatically close (precharge) banks being read from or written to at the end of the transaction. • The user selects whether read or write commands are issued with auto-precharge through the auto_pch signal.

This is Padding… • RDRAM vs. DDR SDRAM • DDR → Double Data Rate DDR II→ Quad Data Rate RDRAM DDR II SDRAM

感謝台下的諸位能聽完~~ 謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家謝謝大家~~